## EFFICIENT SYSTEM-LEVEL FAULT DIAGNOSIS OF LARGE MULTIPROCESSOR SYSTEMS

by

Tamás Bartha M.Sc., Budapest University of Technology and Economics, 1993

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Faculty of Electrical Engineering and Computer Science Budapest University of Technology and Economics

Copyright © 2000 by Tamás Bartha

#### Abstract

### Efficient System-Level Fault Diagnosis of Large Multiprocessor Systems

Tamás Bartha, M.Sc. Budapest University of Technology and Economics, 2000

Supervisor: Prof. Endre Selényi, D.Sc.

This document presents new results in different areas of multiprocessor fault tolerance. The first main topic of research studied is fault diagnosis of large parallel computers. Both the centralized and distributed approach to fault diagnosis are considered. In the framework of centralized diagnosis a novel probabilistic fault diagnostic methodology, called *local information diagnosis* (LID), is introduced. The LID approach combines the diagnostic power of the generalized test invalidation model with the time efficiency of probabilistic methods. The developed methodology is applied to create three classes of diagnostic algorithms: *limited inference*, *limited information*, and *scalar* methods. The representation and handling of the diagnostic information is different in the above classes, providing a diagnostic accuracy/time complexity trade-off.

LID diagnostic algorithms employ the generalized test invalidation model to handle a wide range of testing arrangements and failure behavior. They use parameterized inference rules to obtain one-step diagnostic implications conforming to the fault hypotheses and the actual syndrome. Scalar methods utilize only the one-step implications, thus achieving low time and space complexity together with good diagnostic accuracy. Limited inference and limited information methods generate multiple-step diagnostic implications by transitively propagating one-step implications. They provide significantly better diagnostic accuracy than either scalar or other existing probabilistic algorithms. Naturally, they have higher time and space complexity than scalar methods, but their execution time and memory requirements are still quite adequate for practical application. Different techniques of using the diagnostic implications in the fault classification process are studied in detail. For the purpose of fault classification based on diagnostic implications three heuristic methods having different characteristics are developed and analyzed.

The thesis presents five new probabilistic fault diagnostic algorithms created on the basis of the local information diagnosis methodology. The diagnostic and computational performance of the algorithms are compared using both theoretical analysis and measurement techniques. The measurement result confirm that the new algorithms have better diagnostic accuracy than existing methods, while their time complexity is acceptable for the application in large-scale computing systems. The results also demonstrate that the developed methods are

- flexible

- applicable in non-symmetric and heterogeneous test invalidation situations,

- work in arbitrary system topology, and

- can improve the accuracy of the diagnosis by iteratively extending the amount of diagnostic information extracted from the syndrome.

The thesis also introduces new results in the area of distributed fault diagnosis. An innovative distributed diagnostic algorithm is described, which lays special emphasis on the low induced diagnostic message load during normal operation. The algorithm schedules the higher communication load during the initialization of the system, when the performance requirements are not strict. During the *initial* stage a system-wide local diagnostic image is generated in each processing element. In the later working stage this basic diagnosis is updated incrementally. This diagnostic strategy also supports the event-oriented dissemination of the testing information, therefore new messages are only transmitted if they contain relevant information. The diagnostic procedures are supplemented by two communication protocols, tailored to the characteristics of the two stages of diagnosis.

The third topic of research presented is a backward error recovery scheme developed for a practical system: the APEmille parallel computer. The created recovery scheme unifies the error recovery mechanisms selected for the different components on the basis of a component-level failure semantics model. It is argued that the two main architectural units require distinct recovery approaches, and the main features that determine the applicable solutions are explained in detail. The selection of component-level recovery mechanisms extends to single and multiple failure occurrences in the considered resource. As part of the recovery scheme a prospective implementation of a stable storage is given, which fits into the architecture of the APEmille computer and does not require the inclusion of external hardware components.

## Dedication

To my parents, for their love and support

#### Acknowledgements

This thesis would never have been completed without the support and encouragement of my advisor, Endre Selényi. His insightful comments and constructive criticism taught me to concentrate on the essential aspects of the presented work and helped me to overcome my constant urge of exploring my new ideas without investigating into the depth of old ones.

I am also indebted to András Pataricza, who is a guiding influence of my professional and personal life. I thank him for the possibility to have research opportunities abroad, which helped me to get acquainted with new approaches and to discover new directions.

I express my gratitude to Professor József Bokor for providing me with the ideal conditions to do my work. I would like to thank Professor Piero Maestrini, and Professor Mario Dal Cin for hosting me in their research institutes and making it possible for me to participate in the research projects.

I am grateful to all of my colleagues who collaborated me on various topics or simply shared their opinion of my work with me. In particular, I would like to mention István Majzik, Jörn Altmann, and Stefano Chessa, whose friendship is one of the most important results of the years spent with preparing this thesis.

## Contents

| M            | Motivation |                                                            |                |  |  |  |

|--------------|------------|------------------------------------------------------------|----------------|--|--|--|

| $\mathbf{C}$ | ontri      | bution                                                     | ix             |  |  |  |

| 1            | Inti       | roduction                                                  | 1              |  |  |  |

|              | 1.1        | Overview of multiprocessor fault tolerance                 | 1              |  |  |  |

|              |            | 1.1.1 Dependability impairments                            | 1              |  |  |  |

|              |            | 1.1.2 Means of dependability                               | 3              |  |  |  |

|              |            | 1.1.3 Model and elements of system-level fault diagnosis   | 4              |  |  |  |

|              | 1.2        | System-level fault diagnosis                               | 11             |  |  |  |

|              |            | 1.2.1 Classification of system-level diagnostic algorithms | 14             |  |  |  |

|              |            | 1.2.2 Centralized diagnostic algorithms                    | 17             |  |  |  |

|              |            | 1.2.3 Distributed diagnostic algorithms                    | 24             |  |  |  |

|              |            | 1.2.4 Generalized test invalidation                        | 34             |  |  |  |

| 2            | Cer        | ntralized fault diagnosis 3                                | 39             |  |  |  |

|              | 2.1        | Local information diagnosis                                | 39             |  |  |  |

|              |            | 2.1.1 Inference propagation based approaches               | 12             |  |  |  |

|              |            | 2.1.2 Fault classification heuristics                      | 16             |  |  |  |

|              |            | 2.1.3 Scalar approaches                                    | 19             |  |  |  |

|              | 2.2        | Algorithm properties                                       | 53             |  |  |  |

|              | 2.3        | Measurement conclusions                                    | 30             |  |  |  |

|              | 2.4        | Application of local information diagnosis                 | <sub>32</sub>  |  |  |  |

| 3            | Dis        | tributed fault diagnosis 6                                 | 35             |  |  |  |

|              | 3.1        | Illustrative system: the Parsytec GCel parallel computer   | 35             |  |  |  |

|              | 3.2        | An event-driven distributed diagnostic algorithm           | 72             |  |  |  |

|              |            | 3.2.1 Structure of the distributed algorithm               | 74             |  |  |  |

|              |            | 3.2.2 Implementation details                               | 33             |  |  |  |

|              | 3.3        | Adapting the LID approach to distributed systems           | 35             |  |  |  |

| 4            | Fau        | alt tolerant architecture of large computing systems 9     | )1             |  |  |  |

|              | 4.1        | Illustrative system: the APEmille parallel computer        | 91             |  |  |  |

|              | 4.2        | Built-in support for fault-tolerance in APEmille           | <del>)</del> 6 |  |  |  |

|              | 4.3        | Failure model of APEmille                                  | 98             |  |  |  |

|              | 4.4                                                 | Backward error recovery in APEmille                 | 101  |  |

|--------------|-----------------------------------------------------|-----------------------------------------------------|------|--|

|              |                                                     | 4.4.1 Recovery of APEmille processors               | 103  |  |

|              |                                                     | 4.4.2 Recovery of Global and Local Host computers   | 105  |  |

|              | 4.5                                                 | Integration of local information diagnosis          | 107  |  |

|              | 4.6                                                 | Constraint-based system-level fault diagnosis       |      |  |

| 5            | Con                                                 | nclusions and future work                           | 111  |  |

| A            | Defi                                                | initions and notation                               | A-1  |  |

| В            | Pro                                                 | bability models                                     | B-1  |  |

| $\mathbf{C}$ | Sim                                                 | ulation of the LID algorithms                       | C-1  |  |

|              | C.1                                                 | Measured characteristics                            | C-1  |  |

|              |                                                     | C.1.1 Practical aspects                             | C-1  |  |

|              |                                                     | C.1.2 Theoretical aspects                           | C-5  |  |

|              | C.2                                                 | Measurement results                                 | C-7  |  |

|              |                                                     | C.2.1 Comparison of fault classification heuristics | C-8  |  |

|              |                                                     | C.2.2 Comparison to existing probabilistic methods  | C-13 |  |

| D            | Communication protocols for distributed diagnosis D |                                                     |      |  |

|              | D.1                                                 | Communication in the initial stage                  | D-1  |  |

|              | D.2                                                 | Communication in the working stage                  | D-4  |  |

| $\mathbf{E}$ | Reliable storage in APEmille                        |                                                     |      |  |

| Bi           | bliog                                               | rraphy                                              | xxv  |  |

## List of Tables

| 1.1 | Non-equivalent testing models                             |

|-----|-----------------------------------------------------------|

| 1.2 | Comparison testing model                                  |

| 1.3 | Generalized model of test invalidation                    |

| 1.4 | Parameterized inference rules                             |

| 2.1 | Properties of the LID algorithms                          |

| 2.2 | Measurement activities                                    |

| 3.1 | Fault classification in the distributed algorithm         |

| 3.2 | Test invalidation including interconnection links         |

| 4.1 | Failure model of APEmille components                      |

| 4.2 | Component-level fault tolerance techniques for APEmille   |

| 4.3 | Test invalidation including interconnection links         |

| C.1 | Measured characteristics                                  |

| C.2 | Varying parameters                                        |

| C.3 | Measurement methods                                       |

| C.4 | Measured parameter values                                 |

| C.5 | Maximum misdiagnosed units in group fault patterns        |

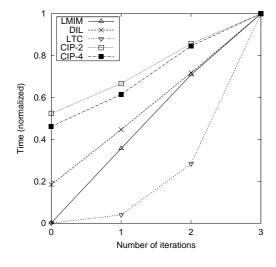

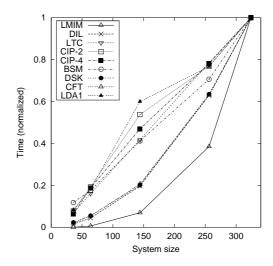

| C.6 | Time complexity versus number of iterations               |

| C.7 | Average misdiagnosed units in various invalidation models |

| C.8 | Time complexity versus system size                        |

| E.1 | Realization of the stable storage properties              |

# List of Figures

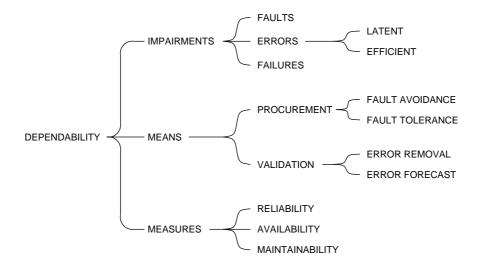

| 1.1  | System dependability and related concepts                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

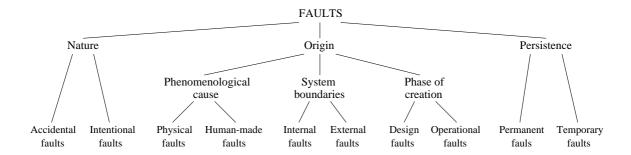

| 1.2  | The classification of faults                                                                                                                                        |

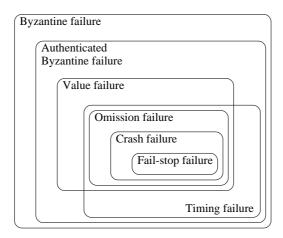

| 1.3  | The relationship of failure classes                                                                                                                                 |

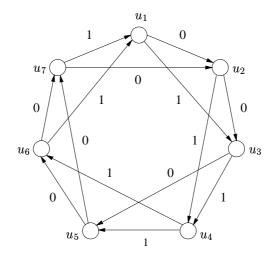

| 1.4  | An example diagnostic situation                                                                                                                                     |

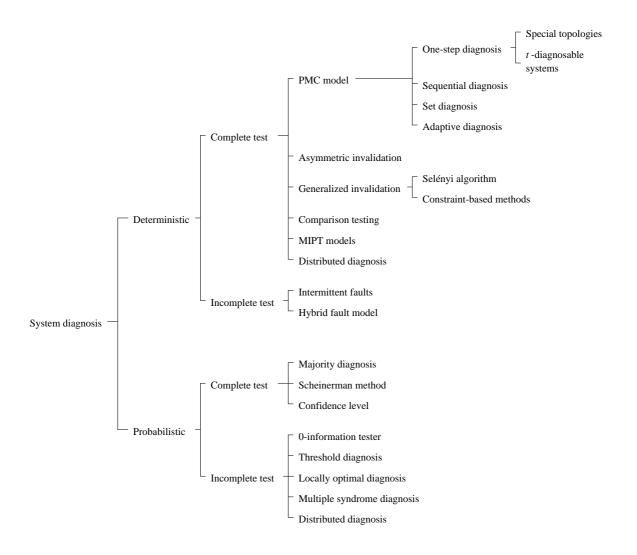

| 1.5  | Classification of main research areas of system-level diagnosis                                                                                                     |

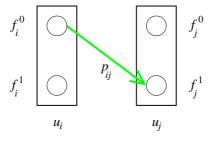

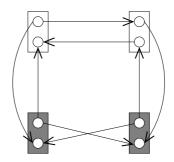

| 1.6  | Components of the inference graph                                                                                                                                   |

| 1.7  | Inference graph creation                                                                                                                                            |

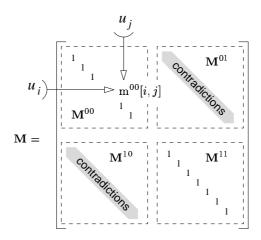

| 1.8  | Structure of the inference matrix                                                                                                                                   |

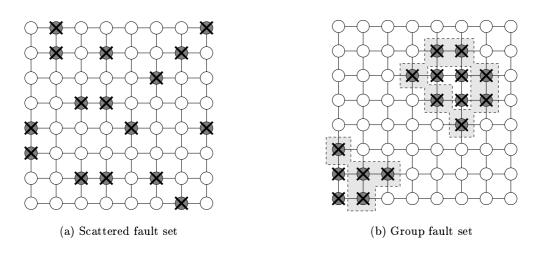

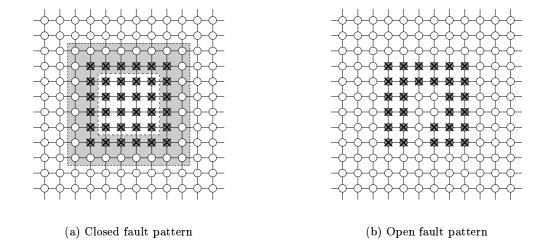

| 2.1  | Example of the two main fault pattern types                                                                                                                         |

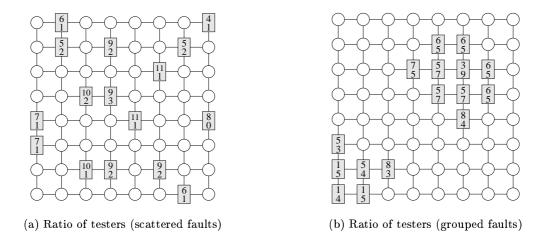

| 2.2  | Ratio of the fault-free/faulty tester processors                                                                                                                    |

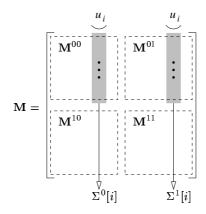

| 2.3  | Calculation of the $\Sigma^0[i]$ and $\Sigma^1[i]$ values                                                                                                           |

| 2.4  | Example for determining the $W$ weight function $\dots \dots \dots$ |

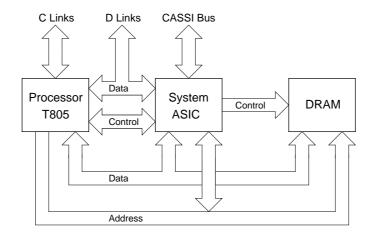

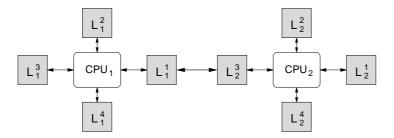

| 3.1  | The structure of a Parsytec GC processing node 6                                                                                                                    |

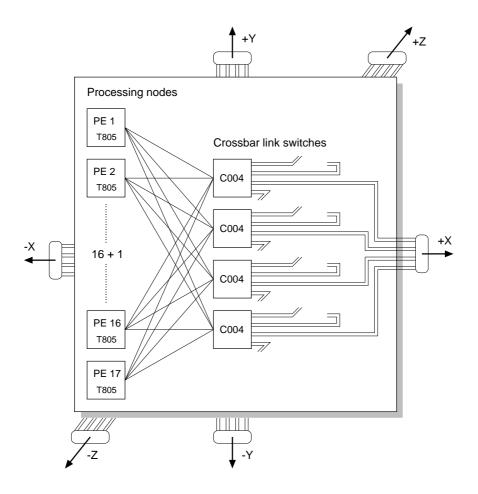

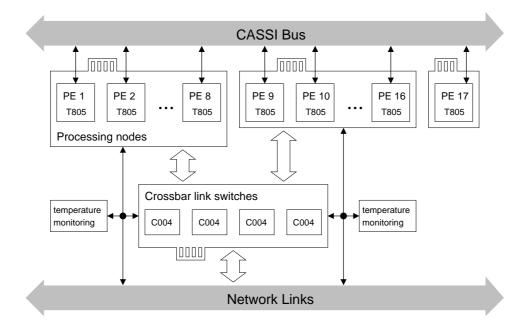

| 3.2  | A Parsytec GC cluster                                                                                                                                               |

| 3.3  | The hardware layout a cluster                                                                                                                                       |

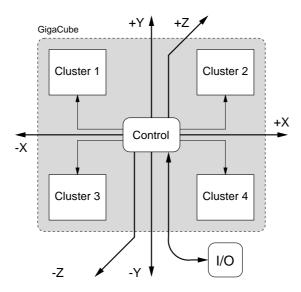

| 3.4  | The logical organization of a GigaCube                                                                                                                              |

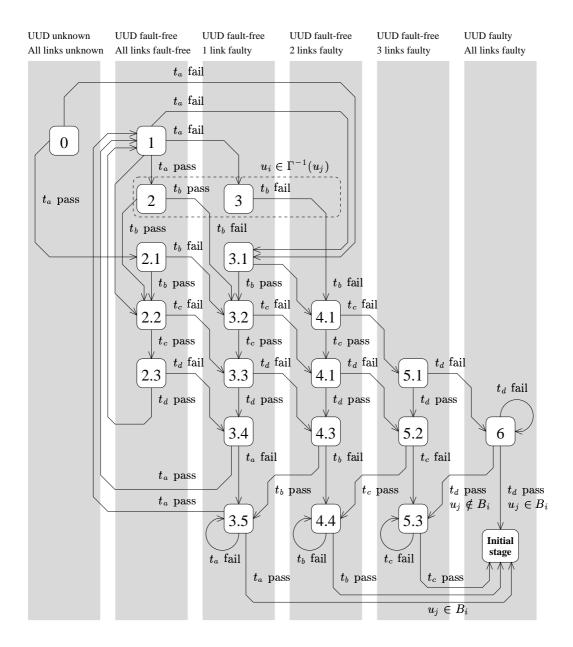

| 3.5  | The fault classification algorithm of the working stage                                                                                                             |

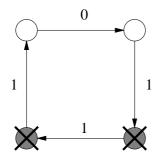

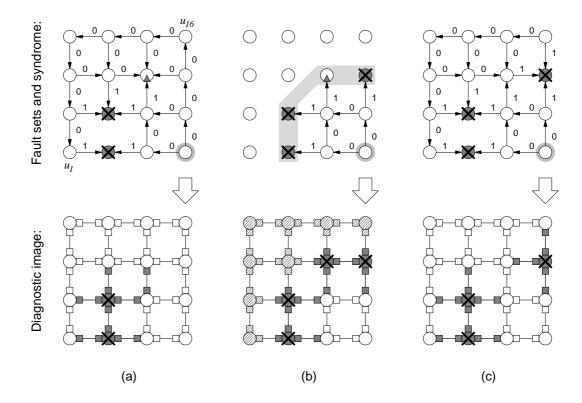

| 3.6  | Distributed diagnostic example                                                                                                                                      |

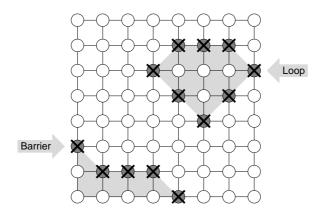

| 3.7  | Barrier and loop                                                                                                                                                    |

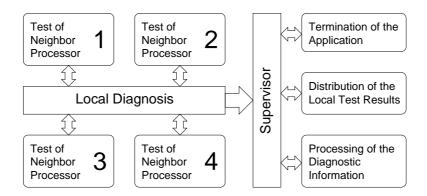

| 3.8  | Software modules of the distributed algorithm                                                                                                                       |

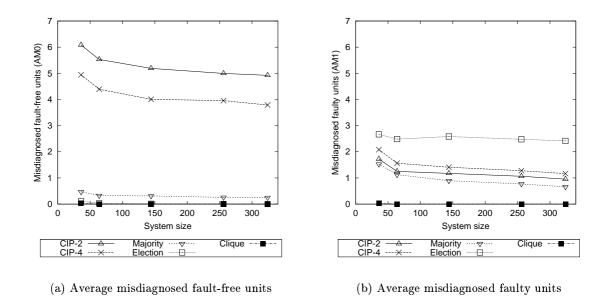

| 3.9  | Average misdiagnosed units in a bordered two-dimensional mesh 8'                                                                                                    |

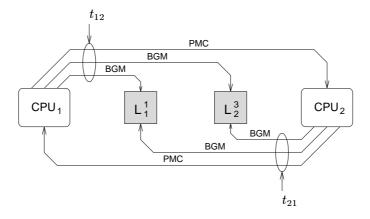

| 3.10 | Parsytec GCel communication scheme                                                                                                                                  |

| 3.11 | Comprehensive test invalidation model of the Parsytec GCel 89                                                                                                       |

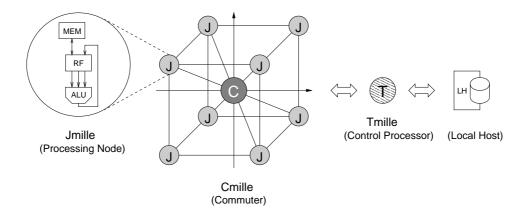

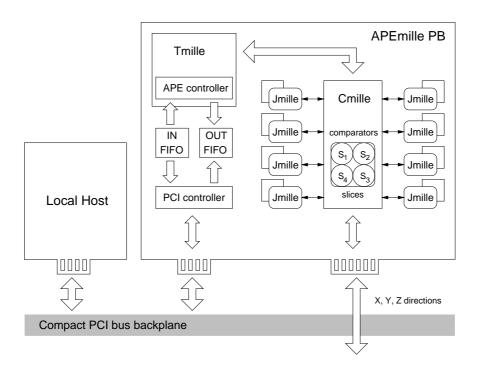

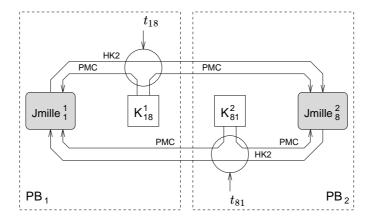

| 4.1  | The logical structure of a Processing Board                                                                                                                         |

| 4.2  | Hardware layout of a Processing Board                                                                                                                               |

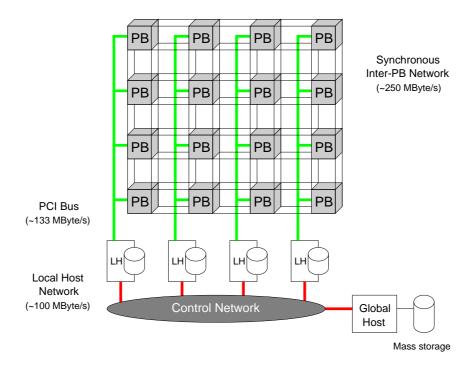

| 4.3  | The APEmille crate                                                                                                                                                  |

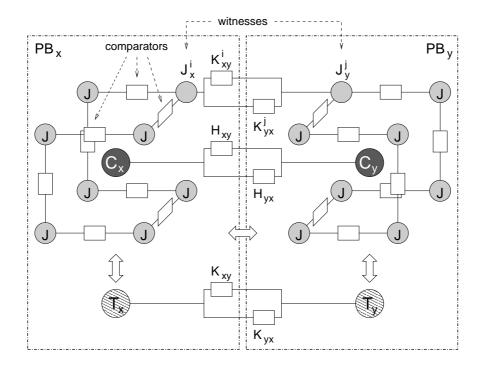

| 4.4  | Testing the components of Processing Boards                                                                                                                         |

| 4.5  | Comprehensive test invalidation model of the Parsytec GCel                                                                                                          |

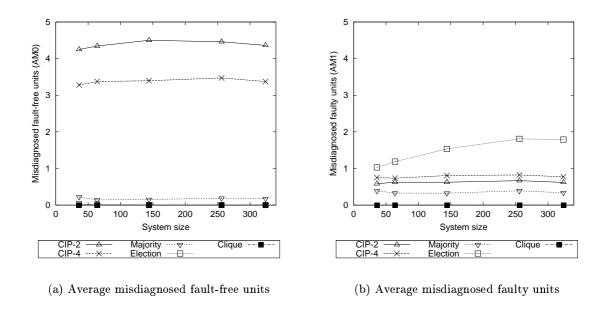

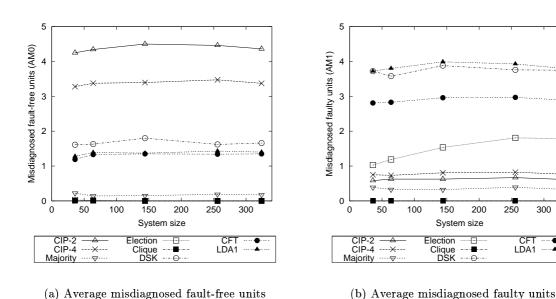

| C.1  | Average misdiagnosed units versus system size                                                                                                                       |

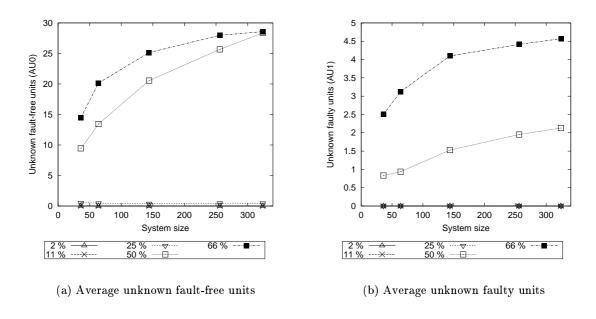

| C.2  | Average unknown classified units by the Clique heuristics                                                                                                           |

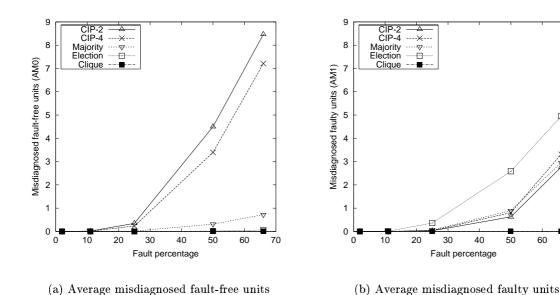

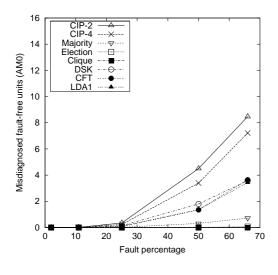

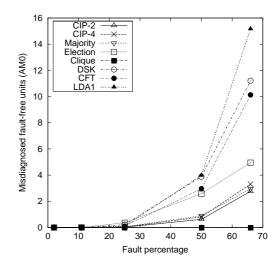

| C.3  | Average misdiagnosed units versus fault set size                                                                                                                    |

| C.4  | Fault patterns to examine diagnosis on the fault group borders C-1:                                                                                                 |

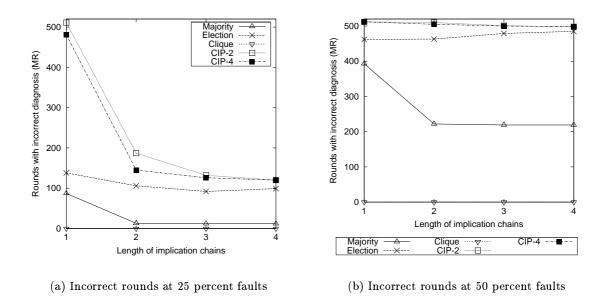

| C.5  | Simulation rounds with incorrect diagnosis versus implication length C-12                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

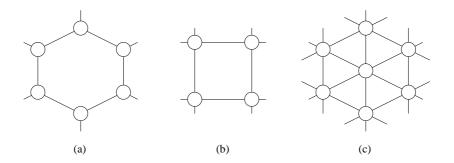

| C.6  | Simulated system topologies                                                                                                                                            |

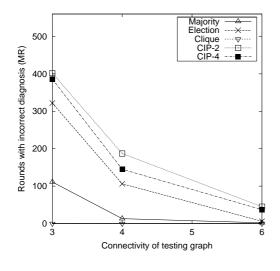

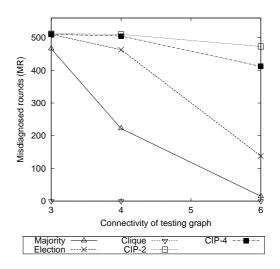

| C.7  | Simulation rounds with incorrect diagnosis versus connectivity C-13                                                                                                    |

| C.8  | Average misdiagnosed units versus system size $\dots \dots \dots$      |

| C.9  | Average misdiagnosed units versus fault set size                                                                                                                       |

| C.10 | Measured time complexity                                                                                                                                               |

|      |                                                                                                                                                                        |

| D.1  | The synchronous communication protocol $\dots$ D-2                                                                                                                     |

| D.2  | Handling irregularity of the interconnection graph $\dots \dots \dots$ |

| D.3  | The asynchronous communication protocol                                                                                                                                |

# List of Algorithms

| 1  | The LMIM algorithm                                      | 43 |

|----|---------------------------------------------------------|----|

| 2  | The DIL algorithm                                       | 44 |

| 3  | The LTC algorithm                                       | 45 |

| 4  | The Majority heuristic                                  | 47 |

| 5  | The Election heuristic                                  | 48 |

| 6  | The Clique heuristic                                    | 50 |

| 7  | The CIP algorithm                                       | 51 |

| 8  | Update phase of the CIP algorithm                       | 52 |

| 9  | The fault classification algorithm of the initial stage | 76 |

| 10 | The barrier detection algorithm                         | 83 |

## Motivation

The rapid development of electronic device manufacturing technology influences the design methodology of high-performance computing systems to a large extent. The present tendency in the price to performance ratio of complex, highly integrated components (like processors, memory chips, and controllers) expedites the use of parallel processing as the primary architectural method for increasing the computational capacity. As a consequence, distributed multiprocessor systems appeared in all application areas of computer technology from networking to financial transaction processing. Massively parallel systems, capable of incorporating as much as several thousand processing elements, represent the most comprehensive utilization of distributed computing. Nowadays workstation clusters start to gain increasing popularity especially in universities and research institutes. These systems require only a high-speed local area network, several low-cost commercial desktop computers, and some (public domain or self-developed) support software which are usually already available in these institutes. Thereby the supercomputer performance of large parallel machines becomes accessible to a growing set of users.

At the same time the requirements of computer system dependability have also increased accordingly, particularly in those application areas, where the continuous error-free operation has serious financial and moral consequences. Such areas are space engineering and research, military technology, medicine, and energetics. While electronic circuits became more reliable with the advances in manufacturing technology, the probability of error occurrence remained significant due to the large amount of built-in components. Since faults will not ever be completely avoidable, computing environments must be equipped with the ability to retain their integrity as experienced by the user in spite of low-level hardware failures. The assurance of system availability is the task of fault tolerance.

There are two main approaches to provide a reliable computing service. A widely used fault tolerance technique is *error compensation*. This approach uses redundant functional units (duplicates, triple-modular redundancy, etc.) to compensate for the loss of the failed devices. The advantage of the approach is its relative simplicity and effectiveness: faults are tolerated transparently, without system down-time or performance degradation. On the other hand, error masking is very expensive: the production cost is at least doubled, not mentioning other important factors like physical dimensions, power consumption, and heat dissipation that also grow accordingly.

Rather than depending on spare units, the other approach called *error recovery* bases on the inherent redundancy of multiprocessor systems. The underlying idea of this approach is to (physically or logically) remove the failed resources and redistribute the user tasks from

the failed units to the remaining fault-free processing elements. Naturally, the decrease of the system resources and the increase of the executed tasks per processor result in a higher overall load and thus computational performance drops. Yet, system availability can be maintained with only a small set of inexpensive additional devices (error detection hardware, switches to isolate the faulty components). Therefore, error recovery is more complex, but less cost-intensive fault tolerance technique than error masking. System-level fault diagnosis is an important part of the error recovery process. Its purpose is to identify the failed components using the results of high-level tests.

The theory of system-level fault diagnosis was founded in 1967 by the introduction of the centralized deterministic fault diagnosis concept [1] of Preparata et al. The name of the concept originates from the high-level modeling of the units constituting the multiprocessor system and their relationship. The diagnostic model comprises processing elements and test connections between them. The testing job is accomplished by the processors of the distributed system themselves, without additional or external tester devices. The fault state of the modeled devices is typically of pass/fail or GO/NO GO type. This simplified view, however, is not disadvantageous within the field of application, as the purpose of diagnosis is localization of faults in the component level and not a detailed report of the underlying hardware phenomenon that caused the failures.

The methodology of centralized deterministic fault diagnosis remained the dominant research area for more than ten years, but the advance of computer architecture created new requirements also for diagnostic algorithms. Changes in the field necessitated the gradual extension of the Preparata model, so new diagnostic approaches appeared to replace the obsolete concepts. New test invalidation models have been developed to describe different relationships between faulty and fault-free units. Parallel to the progress in system organization and complexity increase machines became heterogeneous, therefore only a generalized test invalidation model could capture the new features. The limitations on system structure and admissible fault sets required for complete (classifying every unit) and correct (reflecting the real fault situation) diagnosis made the early algorithms inapplicable in cases where these conditions could not be fulfilled.

The probabilistic diagnostic approach was designed to function in large multiprocessor systems even when the limits of deterministic diagnosability are exceeded. The expansion of the applicability of system-level diagnosis is at the cost of diagnostic accuracy: probabilistic algorithms cannot guarantee the correct and complete classification of each system component, diagnostic mistakes have a non-zero—albeit quite low—probability. Likewise the extensive distributed environments proved that the centralized control of diagnosis causes potential concerns in availability and performance. This problem can be solved by implementing diagnosis with decentralized control, the topic is thoroughly investigated by the theory of distributed system-level diagnosis. Of course numerous other additions and improvements have been devised in the framework of system-level fault diagnosis, the above mentioned approaches are studied in detail within this thesis.

In general the methods existing in the literature contain only a certain aspect of the mentioned extensions. There exists a deterministic algorithm that can handle heterogeneous systems on the basis of the generalized test invalidation model, but that incorporates the limiting conditions of deterministic diagnosability, and is not appropriate for use in massively parallel computers due to its complexity. There exist simple and effective probabilistic algorithms that use only a small portion of the total diagnostic information available in the syndrome and leave the differences of components out of consideration, thus do not estimate the fault state of units very precisely.

Nevertheless, large computing environments usually use many highly integrated communication, control, and monitoring devices. These supplemental devices have a complexity comparable to that of processing elements, therefore it is necessary to involve them in the diagnostic process. However, in such cases the system structure is no longer homogeneous, the diagnostic model must handle variety in the behavior of faulty units. The employed techniques must have small time complexity and low resource usage to handle the huge set of test results collected from the numerous processing elements. The traditional diagnostic t-limit and similar restrictive conditions required for deterministic diagnosis are unmaintainable due to the large dimensions but low local complexity of these systems.

A special class of multiprocessor systems, the massively parallel computers have other important properties that can (and need to) be utilized in diagnosis. These machines have regular physical and interconnection structure in order to retain scalability. The system complexity is small and constant in the local environment of the processing elements. At the same time the major part of relevant diagnostic information originates in this local area. The computational requirements of the diagnostic algorithm can therefore be significantly reduced by examining only the limited environment of a certain unit during its fault classification, instead of the whole system. This is the basic idea of local information diagnosis.

Centralized fault diagnosis is an integral part of a larger procedure, the error removal type of fault tolerance approach. Its results are utilized by each subsequent steps: error confinement, damage assessment, the reconfiguration of the available resources and task redistribution, as well as the recovery from errors by the restoration of a consistent valid global system state. These steps depend on each other, therefore they must be designed and implemented in a unified framework. Although the individual elements of the error recovery process can be realized with the help of methods and ideas taken from the literature, the structure of the recovery process itself is completely application-specific, and so it requires customized methodology. By participating in the APEmille project which aims at the development of a parallel supercomputer, the author was given the opportunity to formulate such an error recovery scheme.

Although the architecture of the APEmille computer is particularly suitable for the application of centralized fault diagnosis, other machines designed according to different requirements are not capable of employing centralized methods. Typically the completely distributed large scale systems containing many autonomous units belong to this category. The use of central units or resources conflicts with the objectives of these computers. Consequently, the need for adapting the diagnostic procedure to the distributed structure of the system came up already in the eighties. The methodology of distributed fault tolerance by Kuhl and Reddy assigned the task of fault diagnosis to the processing elements of the distributed system themselves. The purpose of the diagnostic algorithm is to guarantee the

uniformity and validity of the created diagnostic image in the case of fault-free units. The isolation of the faulty processors is also achieved in a distributed manner: the fault-free units refuse to cooperate with the faulty ones based on the common diagnostic image, thus boycotting them.

In the recent years many distributed fault diagnostic algorithms have been formulated, indicating the importance of this research area. These methods periodically execute tests in a static or adaptive assignment, then disseminate the local test results to every unit by reliable multicast protocols. The processors receive every test result and perform the analysis of the collected global syndrome individually. Existing methods, however, do not give enough consideration to the message volume caused by the distribution of local test results and the actualization of the adaptive testing arrangement. The possibility of improvement is motivated by the technique of incremental checkpointing. Following its basic mechanism the processors can create an initial global diagnostic image and then update only the differences caused by the occurring new diagnostic events (failure, repair). This way the transmission of the diagnostic messages can also be scheduled in an event-oriented way. Therefore only the creation of the initial diagnostic image generates high message volume, which occurs during the start-up phase of the system and thus does not imply additional load during the execution of user applications.

## Contribution

The thesis presents new research results in three main areas of multiprocessor fault tolerance: centralized fault diagnosis, distributed fault diagnosis, and backward error recovery of parallel computing systems. This section summarizes the new results of our work and refers to those parts of the document where the results are described in detail.

Contribution 1. We have developed a new probabilistic diagnostic methodology based on the counting of one-step diagnostic implications in the implication chains supporting a given fault hypothesis. The new approach employs the generalized test invalidation model (in contrast with the probabilistic algorithms known in the literature). This way it is able to identify the failed system components handling the additional diagnostic information inherent to systems having homogeneous non-symmetric and heterogeneous test invalidation [2]. We have defined probabilistic diagnostic algorithms according to the new methodology [3]. We proved, that the developed algorithms have linear time and space complexity, therefore they are particularly suitable for application in large scale systems [4]. The diagnostic methodology and the corresponding new results are introduced in Sections 2.1 and 2.1.3.

- (a) We have defined the inference graph, which represents the one- (and multiple-) step implications extracted from the syndrome on the basis of the generalized model of test invalidation. We gave a probabilistic decision procedure for the classification of the unit fault states [5]. The decision is based on the number of edges in the directed edge sequences ending at a certain node of the inference graph. This quantity is equivalent to the number of diagnostic implications supporting the fault hypothesis corresponding to the given node. The decision making method assumes that fault-free tester units dominate the local environment of the diagnosed unit. Contrasted to existing probabilistic algorithms this new diagnostic approach considers the information originated not only the direct neighbors, but (to a limited depth) at the farther units as well. The utilization of this additional information reflects in improved diagnostic accuracy. (The definition of the inference graph can be found in Section 1.2.4, while the different variants of the probabilistic decision mechanism are described in Sections 2.1.2 and 2.1.3.)

- (b) We have developed an algorithm for the efficient (although distorted) estimation of the basic quantities of the above probabilistic decision making method. The algorithm uses two implication counters to compute the number of elements in the implication chains supporting the fault-free/faulty states of units. Therefore, it is referred to as the

CIP-2 (Count Inference Paths) algorithm [3]. The counter values are determined in multiple iteration step, using only the counters of the neighbor units, thus achieving linear time and space complexity. (The CIP-2 algorithm is one of the scalar LID methods introduced in Section 2.1.3. The theoretical values of time complexity can be found in Section 2.2, while the practical evaluation is presented in Section C.2.)

(c) We have refined the CIP-2 algorithm using four implication counters. The new algorithm, called CIP-4, can differentiate the implication chains not only by their endpoints, but also by their start points. We have modified the probabilistic decision making procedure to consider only implications drawn from the fault-free states of units. This way a better estimation of the fault hypothesis likelihood was obtained and diagnostic accuracy has been improved compared to the CIP-2 algorithm. (The CIP-4 algorithm is the second scalar LID method described in Section 2.1.3. The comparison of the two CIP algorithms can be found in Section C.2.)

The underlying idea of the developed local information diagnostic methodology is that in the case of practical fault set types there is enough information available in the local environment of units to determine the quantities used in the probabilistic decision making procedure with sufficient accuracy. Existing deterministic algorithms typically classify the fault states taking into consideration all of the units in the system. On the other hand, probabilistic algorithms examine only the direct neighbors of the diagnosed unit. Local information diagnosis creates a compromise between these two approaches. The information used in the LID diagnostic process is gathered from a limited, but wider range environment than the direct neighborhood. Therefore, we could derive algorithms with smaller time and space complexity than the existing deterministic methods, while achieving better diagnostic accuracy than existing probabilistic techniques.

For statistical measurement of the CIP algorithm properties we implemented a general-purpose simulation environment. The simulation environment is capable of the verification of each centralized probabilistic diagnostic algorithms developed in the framework of this thesis, as well as the existing centralized algorithms known in the literature. (The description of the simulation environment is not covered by this document due to the many options and detailed measurement results the simulator provides, a brief user's guide is contained in [6].) Both the CIP-2 and CIP-4 algorithms have been implemented within the simulation environment, and their diagnostic properties were studied. We have confirmed that the CIP-4 algorithm provides better diagnostic accuracy than the CIP-2 algorithm [4]. Both algorithms were proved to correctly identify the fault state of those units which can be surely classified based on the syndrome (provided they are run in an adequate number of iterations) [3]. (These theoretical results are explained in Section 2.2, the correctness proof is provided by Theorem 2.2.9.)

Contribution 2. We have developed a new probabilistic diagnostic method based on the limited transitive propagation of one-step diagnostic implications. The method consists of two subsequent phases. In the first phase the one-step diagnostic implications are collected

and they are transitively propagated in a limited depth [7]. The employed data representation includes the entire set of implications, therefore the method is able to extract the complete diagnostic information contained in the syndrome (provided it is executed in an appropriate number of iterations). In the second phase the generated implication set is processed using heuristic fault classification rules [8]. Procedures for both phases of the new diagnostic method have been devised. Using the created procedures we have formulated probabilistic diagnostic algorithms. The developed algorithms were confirmed to have better diagnostic properties than the CIP-2 and CIP-4 algorithms, as well as the probabilistic algorithms known in the literature. The improvement of the diagnostic accuracy comes on the expense of the increase in time and space complexity [4]. The description of the new diagnostic method and the procedures devised for the different phases can be found in Sections 2.1.1 and 2.1.2.

- (a) We have devised a method for the limited-length transitive propagation of diagnostic implications based on matrix multiplication. The method, called the LMIM (Limited Multiplication of Inference Matrix) algorithm, obtains the multiple-step implication set used in probabilistic diagnosis by computing a given power of the implication matrix [9]. The time complexity of the method is  $O(n^3)$  in the function of the system size, which is determined by the employed matrix multiplication. (The LMIM algorithm is one of the limited inference methods defined in Section 2.1.1.)

- (b) We have developed a new method for limited-length transitive propagation of diagnostic implications, which generates a diagnostically equivalent implication set to the matrix multiplication. The new method, called the DIL (Distribution of Inference Lists) algorithm, computes the partial implication set used in local information diagnosis with less time complexity (O(n²) instead of O(n³)) than the LMIM algorithm [2]. The reduction of the time complexity is achieved by realizing the transitive propagation in multiple iterations, using solely the implication sets of the direct neighbor units. (The the DIL algorithm is the other limited inference method described in Section 2.1.1.)

- (c) We have developed a new method for limited-length transitive propagation of diagnostic implications based on the transitive closure of diagnostic implications in a reduced environment. The method has linear time and space complexity in the function of system size. The time complexity depends on the extent of local environment considered in diagnosis at a rate of  $O(\nu_k^3)$ . In large systems and for small considered environments the new method, called the LTC (*Local Transitive Closure*) algorithm, computes the partial implication set used in local information diagnosis more efficiently than the algorithms known in the literature [2]. (The LTC algorithm is a limited information method presented in Section 2.1.1.)

- (d) We have formulated three new heuristic methods for the diagnostic analysis of the generated partial implication set. The *Majority* heuristic classifies the fault state of the diagnosed unit according to a majority decision on the implications drawn from

the fault-free states of the neighbor units. The *Election* heuristic performs the diagnostic task sequentially, by selecting the most likely faulty unit in each iteration step. The Clique heuristic groups units according to the identical and opposite relationship between unit fault hypotheses. Then, it selects the units classified as fault-free by finding the largest group of units having identical and consistent fault states [8]. (The three fault classification heuristics are defined in Section 2.1.2.)

The one-step diagnostic implications obtained from the system based on the actual syndrome can be extended into multiple-step implications utilizing the transitive property. The adaptation of the local information diagnostic methodology in this framework means the limitation of the transitive propagation. We have given two different approaches to solving the problem of limited propagation of diagnostic inferences. The *limited inference* (LMIM, DIL) approach performs the transitive propagation of the whole implication set in a restricted depth. The *limited information* (LTC) approach executes the transitive closure of an implication set generated from a reduced environment [2].

We have shown that the limited inference and limited information approaches generate identical implication sets (though possibly in a different number of iterations). Thus, they are equivalent from the diagnostic viewpoint. (This statement is supported by Theorems 2.2.2, 2.2.4, and 2.2.7 given in Section 2.2.) We have demonstrated by simulation experiments, that the computation of the transitively extended diagnostic implication set by the matrix multiplication technique (known in the literature and employed by the LMIM algorithm) performs many redundant operations in large, regular topology multiprocessor systems. The devised alternative methods (DIL, LTC) have much better suited time complexity for practical applications [4].

The formulated heuristic fault classification methods are essentially the applications of the probabilistic decision making procedure defined in Contribution 1. We have created new probabilistic diagnostic algorithms combining the LMIM, DIL, and LTC implication propagation methods and the Majority, Election, and Clique fault classification heuristics. We have appointed the characteristics affecting the diagnostic accuracy of heuristics. With the help of the simulation environment the developed fault classification heuristics were compared to each other, and to several probabilistic diagnostic algorithms taken from the literature [8]. The measurements have confirmed that the new algorithms are better than the existing methods in terms of the selected characteristics up to one order of magnitude. The improvement is particularly large in systems with non-symmetric and heterogeneous test invalidation [4]. (The measurement activities and the obtained results for the developed and existing algorithms are described in detail in Appendix C.)

Contribution 3. We have developed a new, general-purpose distributed diagnostic algorithm. The new algorithm combines the static and event-oriented diagnostic approaches existing separately in known algorithms, in order to reduce the induced message load [10]. The algorithm consists of two main stages. The initial stage is executed in the startup period shortly after the system was switched on. Its main purpose is to determine the actual fault state of the whole system. The second, working stage is active during the execution of user

applications. Its objective is to handle the occurring failure events with smaller diagnostic message overhead compared to the methods known in the literature [11]. The developed distributed fault diagnostic algorithm, including the two operating stages, is presented in Section 3.2.

- (a) We have defined a diagnostic procedure for the *initial stage* which can quickly produce a consistent global diagnostic image in each fault-free processor. The procedure generates a relatively high message load, however, in the startup period the performance requirements are not strict. On the other hand, the time complexity of the procedure is not adversely affected by the existence of a large number of faulty units (contrasted to the known event-oriented algorithms) [12].

- (b) We have defined a diagnostic procedure for the working stage which analyzes only the changes in the syndrome incrementally, compared to the global diagnostic image created in the initial stage. The distribution of the testing information is accomplished by an event-oriented mechanism in order to decrease the transmitted message volume. Diagnostic messages are started only in the case of detected new diagnostic events (failure, repair), therefore the algorithm influences the system operation during user application execution at a minimum level [12].

- (c) We have determined those situations, in which the incremental approach used in the working stage may lead to an inconsistent diagnostic image. Such situations are handled by returning to the initial stage of the algorithm [11]. (The operation of the initial and working stages, and the conditions controlling the alternation between them are detailed in Section 3.2.1.)

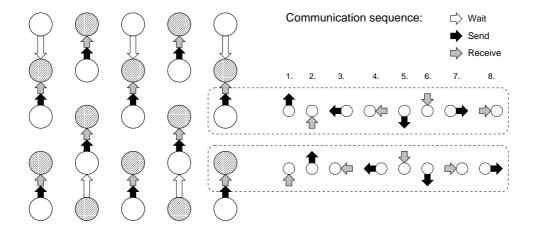

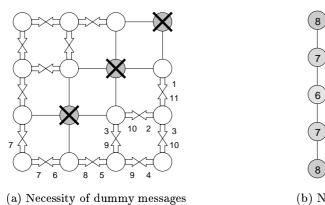

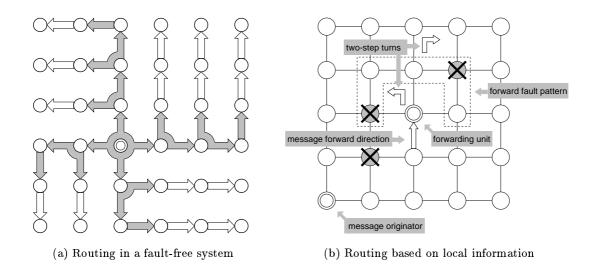

Due to the machine-specific nature of distributed diagnosis the message communication protocols constitute an integral part of the diagnostic algorithm. The two stages of the developed distributed algorithm require different protocols. We have defined an effective, but tightly scheduled synchronous communication protocol for use in the initial stage. (The synchronous communication protocol is specified in Section D.1.) For the purposes of the working stage we have developed an asynchronous communication protocol in order to avoid deadlocks and scheduling problems. The asynchronous protocol has been adopted to the two-dimensional mesh topology of the Parsytec GCel machine. This refined protocol generates nearly optimum number of messages even in the presence of faulty units in the system. (The asynchronous communication protocol is outlined in Section D.2.) The operation of the developed distributed diagnostic algorithm and the employed communication protocols was verified by an experimental implementation in the Parsytec GCel system. (Some details of the practical implementation are covered by Section 3.2.2. Other particulars, not included in this document for the sake of conciseness, can be found in [13].)

We have studied the possibility and requirements of the application of local information diagnostic algorithms in distributed environments were studied. We gave methods for integration of the limited transitive propagation based probabilistic diagnostic algorithms into the developed distributed algorithm. We have examined the possibility of further decreasing the transmitted message volume by limiting the area of message dissemination and showed the effect of the reduced testing information on diagnostic accuracy. (The adaptation of LID algorithms to the distributed environment, and the influence of testing information reduction are presented in Section 3.3.)

Contribution 4. APEmille is a Single Instruction Multiple Data parallel computer prepared as a joint collaboration of several European research institutes. We have developed a comprehensive backward error recovery mechanism that forms a part of the fault-tolerant architecture of the APEmille machine [14]. We have created a component-level failure model of the system, and devised the state saving and state restoration procedures for each component based on this model. In the procedures separate methods were formulated for the case of single and multiple failures [15]. The results concerning the developed recovery mechanism are summarized in Sections 4.3 and 4.4.

- (a) The two main functional units of the APEmille system, the processing engine (SIMD part) and the supervisor computers (MIMD part), must be treated differently with regard to the recovery mechanism. We have devised separate recovery schemes for both parts, taking into consideration the employed diagnostic algorithm and the planned maintenance strategy [16]. (The recovery scheme for the SIMD part is given in Section 4.4.1, while for the MIMD part it can be found in Section 4.4.2.)

- (b) We have developed a prospective implementation of a stable storage, used in the recovery mechanism for reliable recording of state information [17]. The proposed implementation utilizes only the available hardware resources of the system. (The structure of the developed stable storage is described in Appendix E.)

The results corresponding to the contribution are the first steps in the realization of the APEmille backward error recovery mechanism. As this work is not preceded by other research within the framework of the APEmille project, the author had to solve problems outside of the scope of recovery, like the formulation of a simplified, component-level failure semantics model for APEmille (which is included in Section 4.3). The work on the recovery mechanism started at an advanced stage of the project, when it was no longer feasible to suggest modifications in the hardware design. Therefore, one of the requirements during the development of the state saving and state restoration procedures was to employ only the available hardware resources.

Although the diagnostic algorithm, which constitutes a part of the recovery mechanism, has already been completed by the time we started working on the topic of recovery, the APEmille computer is also an appropriate platform for the application of local information diagnosis. Thus, we examined the possibility and conditions of integration of the LID probabilistic diagnostic methods in the fault tolerance of APEmille. (The integration problems and solutions are explained in Section 4.5.)

## Chapter 1

## Introduction

This chapter introduces the principles and means of fault-tolerant computing with respect to multiprocessor fault tolerance. The basic notions and definitions are presented through the *dependability concept* of Laprie [18]. A set of selected centralized and distributed fault diagnostic algorithms are outlined to illustrate the main problems and existing solutions to the task of fault diagnosis. Finally, the concept of generalized test invalidation and its use for system-level fault diagnosis is described.

### 1.1 Overview of multiprocessor fault tolerance

Computer system dependability is the quality of the delivered service such that reliance can justifiably be placed on this service. The delivered service is an abstraction of the system behavior as it is perceived by other systems (its users) interacting with the considered system. This abstraction is highly dependent on the application, for example time plays an important role in the abstraction, as the time granularity for the system and its users are generally different.

#### 1.1.1 Dependability impairments

The *impairments* of dependability are undesired circumstances causing or resulting the lack of dependability, whereby reliance cannot be justifiably placed on the service any more. Reasons, causing the loss of dependability manifest in the forms of faults, errors, and failures:

- 1. a fault is the cause (in its phenomenological sense) of an error,

- 2. an *error* is the part of the system state which is responsible for the manifested failure (i.e., the delivery of a service not complying with the specification), and

- 3. a failure occurs when the delivered service differs from the expected service, where the expected service is described in the service specification. The failure occurred because the system was erroneous.

Upon occurrence, a fault creates a latent error, which becomes an effective error upon activation. When the effective error modifies the delivered service, a failure occurs. For example, a short circuit occurring in an integrated circuit is a fault, the consequence (modification of

Figure 1.1: System dependability and related concepts

the circuit function) is a latent error. When the module where the error resides is activated (an appropriate input pattern selects the erroneous function) the error becomes effective. This effective error may produce incorrect data (value of results or timing of their delivery) which may affects the delivered service creating a failure. Definitions of fault, error and failure can be stated in other terms as: an error is the manifestation in the system of a fault, and a failure is the manifestation on the service of an error. The granularity of a particular dependability model always stops at the cause which is intended to be avoided or tolerated. Otherwise, a faults would become nothing else than a failure of a system having interacted with the considered system.

Faults can be categorized into the classes of *physical faults*: adverse physical phenomena, either internal (threshold changes, short circuits) or external (environmental effects), and *human-made* faults: imperfections, which may be either design faults (committed during the system design and modifications) or interaction faults (violations of operating or maintenance procedures).

The life of a system is perceived by its users as an alternation between service accomplishment (the service is delivered as specified) and service interruption (the delivered and specified services differ). The events causing transition between the above two system states are the failure and restoration (also referred to as repair). Quantification of the characteristics of this accomplishment/interruption alternation leads to three possible measures of dependability. Reliability measures the continuous service accomplishment (or equivalently the time to failure) from a reference initial instant. Availability rates the service completion with respect to the alteration of accomplishment and interruption. Maintainability quantifies the continuous service interruption (or equivalently the time to restoration). These characteristics depend on non-deterministic, stochastic processes, so they can be represented mathematically as probabilities.

The error latency duration may vary considerably, depending upon the fault, the system utilization and other circumstances. Whether or not an error will lead to a failure is determined by the activation conditions that cause a latent error to become effective, the

system construction with the regard of available redundancy, and the definition of a failure from the users point of view (for example, voltage threshold levels in logical circuits imply the notion of "error acceptance regions"). Available redundancy can be classified as

- 1. explicit redundancy, built-in the system in order to ensure fault-tolerance, i.e., it is directly employed to prevent an error from leading to a failure, and

- 2. *implicit redundancy*, the level of redundancy residing in every system, which may play the same role as explicit redundancy. It is in fact difficult to build a system without any form of redundancy.

#### 1.1.2 Means of dependability

Constructing a dependable computing system requires the combined utilization of a set of methods, which can be either fault-avoiding, preventing the occurrence of faults by appropriate construction of the system, or fault-tolerant, utilizing the implicit redundancy in a computing system to deliver the specified service in spite of that faults have occurred, error-removing, trying to minimize the presence of latent errors so they cannot be activated, or error-forecasting, estimating the presence, creation and consequences of errors by evaluation. The former two groups may be regarded as constituting dependability procurement, attempting to provide the system with the ability to deliver service complying with its specification, while the latter two groups may be considered as constituting dependability validation, aiming at reaching confidence in the system ability to deliver the specified service.

Fault-tolerance is carried out by error processing, which may be automatic or operator assisted. The purpose of error processing is the preservation of data integrity. Two constituent phases can be recognized: (1) effective error processing, bringing the effective error back to a latent state (if possible, back to the state right before the occurrence of the failure), (2) latent error processing, ensuring that a latent error does not become effective (again). This is carried out by making the error passive and reconfiguring the system to make it capable of delivering the specified service. Effective error processing can be realized either as error compensation, where the fault affected system component contains enough redundancy to fulfill the delivery of an error-free service despite the erroneous internal state, or error recovery, where an error-free state is substituted for the erroneous state.

Prior to error processing the erroneous state must be recognized (as early as possible), which is the task of error detection. On the other hand, error compensation may be applied systematically even in the absence of effective errors. This systematic application is called error masking, and it ensures that any effective error (that was taken into account during the design process) is brought back to a latent state. As an example, a logical AND gate can be protected of a single stuck-at-1 fault by a wired OR connection of duplicated AND gates. This way either of the two AND gates can independently pull down the output and realize the logical function. However, error masking can at the same time result an unregarded decrease of redundancy. This is well demonstrated by our example, as there is no information if none, one, or both of the duplicated AND gates became faulty during the operation of the system. Therefore, practical implementations of error masking generally

involve error detection. This way error compensation can be applied again when an effective error has been detected, in order to check if latent error processing has to be executed.

The substitution of an error-free state for the erroneous state may be carried out in two directions: backward or forward. Backward error recovery transforms the erroneous system state into a previously occurred valid system state prior to the error becoming effective. Forward error recovery finds a new valid system state instead of the erroneous system state, which has never occurred or which at least has not occurred since the same erroneous state. In forward error recovery the damage caused by a detected error must be assessed. Damage assessment can be omitted in the case of backward recovery, provided that the mechanisms enabling the replacement of the erroneous state to a valid state have not been affected by the present faults.

Error processing is generally achieved by maintenance, which is aimed at removing latent errors. Maintenance actions can be *corrective*, removing the latent errors that became effective and have been processed, and *preventive*, eliminating latent errors before they become effective in the considered system. These latent errors can be the results of either physical faults occurred since the last maintenance action, or design faults led to effective errors in other similar systems. The classes of faults which can be tolerated depend on the fault hypothesis considered in the design process, and thus rely on the independence of the implicit or explicit redundancy from the fault creation and activation processes. The mechanisms being liable for fault-tolerance must be protected against the faults affecting them (e.g., voter replication, self-checking observers, stable memory for recovery programs and data [19]). Some system properties, like structural regularity, may limit the necessary amount of redundancy [20]. These properties directly affect the fault model of the system, and so indirectly the set of tolerated faults will also be influenced by them.

The necessary operational time overhead for effective error processing significantly differs in the two main prevention concepts. In error masking, the time overhead is constant, and in practice the duration of error compensation is much shorter than error recovery, due to the larger amount of redundancy. In error detection and recovery, the time overhead is longer when an error becomes effective than when it was latent (it is related to the preparation of recovery points). These characteristics of error processing constrain the applicable fault tolerance methods with respect to the user time granularity. On the other hand, they introduce a relation between operational time overhead and structural redundancy, in its most simple form: "the more the redundancy in the system structure, the less the operational time overhead incurred."

#### 1.1.3 Model and elements of system-level fault diagnosis

System-level fault diagnosis uses a simplified system model composed of units, connections, faults, and tests. The system is built of units called processing elements (PEs) connected by interconnection links. The units execute independent tasks and cooperate with other units using messages. A unit can either be fault-free or faulty. Faults in the system are uncovered using system-level tests performed by the units on adjacent units or neighbors, directly accessible via an interconnection link. The collection of system-level test results is

Figure 1.2: The classification of faults

the *syndrome*. The diagnostic process is the analysis of the syndrome in order to identify the faulty units.

**Faults.** Faults are undesirable—but preferably not unexpected—circumstances negatively affecting the service a system delivers. The sources of faults may be classified according to three main viewpoints: their *nature*, their *origin*, and their *persistence*. The main fault classes according to the three viewpoints [21] are presented in Figure 1.2.

System-level diagnosis distinguishes the following main fault categories:

**Permanent faults.** Permanent faults remain to exist after their occurrence until the related faulty component is repaired, or replaced. Their presence is not affected by point-wise conditions, thus they always produce errors when they are fully exercised. Internal physical or design faults belong to this category.

Intermittent faults. Intermittent faults are temporary internal faults. These faults are essentially permanent faults, but their activation depends on rare combinations of conditions. By their nature, intermittent faults do not occur consistently, which makes their detection a probabilistic event over time. Recurrent faults, whose activating conditions can be reproduced are also considered as intermittent faults in system-level diagnosis.

Transient faults. Transient faults are temporary external faults. They originate from the effects of the physical environment. Transient faults only affect the operation temporarily, usually without causing a permanent fault in the corresponding component. This fault class is hard to deal with in system-level diagnosis. Transient faults cannot be distinguished from intermittent faults just by simply observing the system. However, the difference is very important: the affected component cannot be declared faulty if a transient fault occurred (although a restart or a temporary shutdown might be necessary to restore the integrity of the system).

**Hybrid-fault model.** Transient and intermittent faults are the major source of errors in systems. Recent studies have shown, that generally more than 80 percent of the field failures were caused by these fault types [22]. Therefore, Mallela and Masson [23] introduced the concept of a *hybrid-fault* situation. The hybrid-fault model specifies bounded combinations of permanently faulty and intermittently faulty components in

Figure 1.3: The relationship of failure classes

the system. The concept includes as special cases the case where each faulty unit may only be either permanently or intermittently faulty.

A system generally does not always fail in the same way. The ways a system can fail are specified as its failure modes [24]. They also may be categorized according to different viewpoints. The two main viewpoints significant in system-level diagnosis are the failure domain viewpoint, and the failure perception viewpoint [21]. From the failure domain viewpoint one can distinguish: value failures, when the value of the delivered service does not comply with the specification, and timing failures, if the service is not delivered within the specified response time frame. The latter class is sometimes called a performance failure. Early and late timing failures can be defined depending on whether the service was delivered before or after the specification. A class of failures relating to both value and timing failures are the stopping failures: the system activity is not any more perceptible and a constant value service is delivered. The special case of stopping failures when no service is delivered is called omission failures. If the omission of service delivery is persistent, a crash failure has occurred. The relationship of these failure classes is illustrated in Figure 1.3.

When a failed service is delivered to multiple users, the failure perception leads one to distinguish consistent failures, if all users have the same perception of the failure, or inconsistent failures, when the system users may have different perception of the same failure. Inconsistent failures are usually termed as Byzantine failures, because in this failure class a faulty processor may send different messages to its neighbors during the broadcast of a given piece of information [25]. Since any fault is possible within the Byzantine model, this failure class can be considered the universal fault set. Authenticated Byzantine failures constitute a subclass of Byzantine failures, where messages sent by processors are authenticated and even a failed sender unit cannot imperceptibly alter an authenticated message.

**Tests.** Testing is a *dynamic verification* of the system. A test, in a general sense, can be imagined as the application of some sequence of input patterns and the observation of one or more outputs for one or more time frames [26]. Tests are aimed at uncovering active faults by detecting the errors they caused. The generation of the test inputs can be either deterministic or probabilistic:

| Notation                   | $\mathbf{Name}$          | ${f Reference}$ | Test outcome              |                             |                     |                       |

|----------------------------|--------------------------|-----------------|---------------------------|-----------------------------|---------------------|-----------------------|

|                            |                          |                 | $\odot \rightarrow \odot$ | $\odot \rightarrow \otimes$ | $\otimes \to \odot$ | $\otimes \to \otimes$ |

| $T_{00}$                   | 0-fail-safe tester       |                 | 0                         | 1                           | 0                   | 0                     |

| $\mathrm{T}_{01}$          | perfect tester           |                 | 0                         | 1                           | 0                   | 1                     |

| $\mathrm{T}_{0\mathrm{X}}$ | sequential tester        |                 | 0                         | 1                           | 0                   | $\mathbf{X}$          |

| $\mathrm{T}_{11}$          | irreflexive invalidation | HK2 [28]        | 0                         | 1                           | 1                   | 1                     |

|                            | $(1-fail-safe\ tester)$  |                 |                           |                             |                     |                       |

| $\mathrm{T}_{1\mathrm{X}}$ | reflexive invalidation   | HK1 [28]        | 0                         | 1                           | 1                   | $\mathbf{X}$          |

| $\mathrm{T_{X1}}$          | asymmetric invalidation  | BGM [29]        | 0                         | 1                           | X                   | 1                     |

| $\mathrm{T}_{\mathrm{XX}}$ | symmetric invalidation   | PMC [1]         | 0                         | 1                           | X                   | $\mathbf{X}$          |

| $T_{\mathrm{PT}}$          | partial tester           |                 | 0                         | X                           | X                   | X                     |

| $\mathrm{T}_{\emptyset}$   | 0-information tester     | Blount [30]     | X                         | X                           | X                   | X                     |

Table 1.1: Non-equivalent testing models according to [27]

$\odot$  fault-free unit,  $\otimes$  faulty unit,  $\rightarrow$  test assignment

**Deterministic testing.** Test patterns are predetermined according to the adopted criteria and the given fault model. Test generation can be *functional* or *structural*, depending on whether the selection process is related to the function or the structure of the system.

Random, or statistical testing. Test patterns are selected on the basis of a defined probability distribution on the input domain. The distribution and the number of input patterns are determined according to the adopted criteria and the given fault model.

A test is said to be *complete* for a certain fault if it always fails when the fault is present, and passes when all faults are absent. On the system level, a test performed by unit  $u_i$  on unit  $u_j$  is complete if it detects all low-level faults that can cause a failure in unit  $u_j$ . Yet, for highly complex components such as processors exhaustive testing can take a lot of time and processing capacity, and still not produce accurate results. If the  $t_i$  test detects only the subset  $F^d \subset \mathcal{F}, |F^d| = \phi^d$  of faults from the set of all possible faults  $\mathcal{F}, |\mathcal{F}| = n$ , it is called *incomplete*. The performance of  $t_i$  can be characterized by the *test coverage*, defined as  $cov(t_i) = \phi^d/n$ . Naturally, complete tests have 100 percent test coverage. A second problem that reduces the effectiveness of tests is *test invalidation*. Ideally, the outcome of a test on a fault is not influenced by the presence or absence of other faults. A complete test is called *invalid* if some faults can make it erroneously pass when the fault (for which the test is complete) exists, or can make it erroneously fail when the same fault does not exist.

The phenomena of testing impairment (incompleteness, invalidation) is determined by the behavior of the (faulty) tester unit (i.e., its failure semantic [24]) and the relationship of the tester and tested units. Table 1.1 presents a complete tabulation of the non-equivalent testing models. The table lists the test result in the four possible configurations, respective to the fault state of the tester and tested units. The test result is denoted by 0 if it has passed, 1 if it has failed, and  $X \in \{0,1\}$  if the test result may be arbitrarily pass or fail in the same fault situation.

Test invalidation models are also strongly dependent on the applied testing mechanisms.

The most commonly used testing mechanisms are:

Direct testing. In direct testing, the units of the system execute tests on each other. Typically, unit  $u_i$  tests unit  $u_j$  by giving it certain input sequences and comparing the resulting output sequences with the set of correct responses. Usually only the normal communication facilities can be used for testing purposes. Since units are able to execute the tests individually, these tests can be invalidated only by a fault in the tester unit. This is also known as single invalidation per test (SIPT).

Self-testing. Testing can also be performed by each processing element on itself in a series of *self-tests*. Kuhl and Reddy proposed a hierarchical system of built-in fault tolerance techniques and monitoring devices [31]. These include hardware or software checkers, watchdog timers and processors, error-checking codes, or redundancy with voting. Thus, the testing of a unit becomes a simple request to the built-in self-test component for the actual fault status of the tested unit.

Comparison testing. A practical method of detecting faults in components is performed by comparison. Two or more units are assigned the same task and the output of the task execution of each unit are compared to each other. A difference in comparing the results of two units signifies an error in one or both of them, but there is no way to tell which one of the units is/are faulty. Using comparison testing and n-multiple redundancy (NMR) techniques up to  $\lceil n/2 \rceil - 1$  errors can be tolerated.

While direct testing is mostly performed periodically in dedicated testing sessions between normal system activities, comparison tests can take place concurrently to productive tasks. An error is detected immediately upon propagation. Comparison tests can be made more compact by creating and comparing *signatures* of the results, such as checksums or *cyclic redundancy checking* (CRC) codes.

Multiple invalidation per test. A test may consist of a large number of stimuli to obtain a good test coverage. Testing can be done by a single unit, but as another possibility, it can be the result of cooperation among multiple testing units. In the latter case a fault in any of the participating units can invalidate the result. If the failure of more than one independent modules can invalidate a test, the test invalidation model is follows a multiple invalidation per test (MIPT) scheme.

Time domain testing. A large portion of the potential failures manifests in the time domain (see Figure 1.3). Therefore, it is necessary to also test the behavior of system components with respect to time. When a unit fails to complete a task by a certain deadline, or a message is not received within a certain time frame, a timing failure occurs. Errors causing timing failures can be detected using time stamps and watchdog timers. The consistency of time domain testing usually requires the presence of a global set of synchronized clocks. A common time domain testing technique is the use of < I'm alive > or "heartbeat" messages. In this technique units periodically send < I'm alive > messages to their neighbors, and validate the incoming messages