#### PhD Thesis:

# Constraint-Based Architectural Test Pattern Generation

#### Balázs Sallay

Department of Measurement and Information Systems Budapest University of Technology and Economics H-1521 Budapest, Műegyetem rkp. 9, Hungary

April 8, 2000

#### Advisor:

Associate Prof. András Pataricza Department of Measurement and Information Systems Budapest University of Technology and Economics

# Contents

| 1 | Inti           | roducti                  | on                                                 | 1 |

|---|----------------|--------------------------|----------------------------------------------------|---|

|   | 1.1            | Cost fa                  | actors in testing                                  | 1 |

|   | 1.2            | Proble                   | m statement and contribution                       | 2 |

|   |                | 1.2.1                    | Test computation goals                             | 3 |

|   |                | 1.2.2                    | Contribution of BudaTest                           | 5 |

|   |                | 1.2.3                    | Test execution goals                               | 5 |

|   |                | 1.2.4                    | Contribution in WST                                | 7 |

|   | 1.3            | Enviro                   | nment and terminology                              | 8 |

|   | 1.4            | Outline                  | e of the thesis                                    | C |

| 2 | Cur            | rent tr                  | ends in digital design                             | 2 |

|   | 2.1            | CAD t                    | ool features                                       | 2 |

|   | 2.2            | Digital                  | design flow                                        | 3 |

|   |                | 2.2.1                    | Synthesizable behavioural VHDL                     | 4 |

|   |                | 2.2.2                    | High-level synthesis                               | 4 |

|   |                | 2.2.3                    | Architectural VHDL                                 | 6 |

|   |                | 2.2.4                    | Low-level synthesis                                | 6 |

|   |                | 2.2.5                    | Gate-level descriptions                            | 7 |

| 3 | $\mathbf{Pre}$ | vious A                  | ATPG approaches                                    | 9 |

|   | 3.1            | Fault r                  | $egin{array}{cccccccccccccccccccccccccccccccccccc$ | 9 |

|   | 3.2            | $\operatorname{Gate-le}$ | evel ATPG                                          | 9 |

|   |                | 3.2.1                    | Gate-level fault model                             | C |

|   |                | 3.2.2                    | Gate-level ATPG algorithms                         | C |

|   |                | 3.2.3                    | Implication                                        | 3 |

|   |                | 3.2.4                    | Sequential extension                               | 3 |

|   |                | 3.2.5                    | CONTEST                                            | 4 |

|   |                | 3.2.6                    | Algorithm evaluation                               | 5 |

|   | 3.3            | High-le                  | evel ATPG approaches                               | 5 |

|   |                | 3.3.1                    | Architectural approaches                           | 5 |

|   |                | 3.3.2                    | Hierarchical testing                               | 7 |

|   |                | 3.3.3                    | Behavioural approaches                             | 9 |

iv CONTENTS

|   | 3.4           | Buda    | 1est objectives                        | <br>• | 31   |

|---|---------------|---------|----------------------------------------|-------|------|

| 4 | Cor           | ıstrain | nt-based modelling                     |       | 33   |

|   | 4.1           |         | definition                             |       |      |

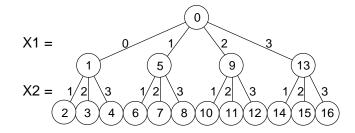

|   | 4.2           | CSP s   | solution                               |       | 35   |

|   |               | 4.2.1   | Backtracking                           |       | 35   |

|   |               | 4.2.2   | The decision tree                      |       | 36   |

|   | 4.3           | Existin | ing CSP solving methods                |       | 37   |

|   |               | 4.3.1   | CSP preprocessing techniques           |       | 38   |

|   |               | 4.3.2   | Forward schemes                        |       | 38   |

|   |               | 4.3.3   | Backward schemes                       |       | 39   |

|   | 4.4           | Const   | raint-based ATPG modelling in CONTEST  |       | 40   |

|   |               | 4.4.1   | ATPG problem representation in CONTEST |       | 41   |

|   |               | 4.4.2   | CSP solving in CONTEST                 |       | 42   |

| 5 | $\mathbf{AT}$ | PG mo   | odelling in BudaTest                   |       | 43   |

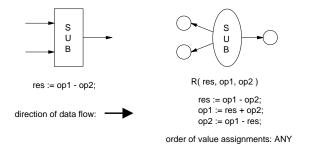

|   | 5.1           | The co  | constraint network                     |       | 43   |

|   |               | 5.1.1   | Variable representation                |       | 43   |

|   |               | 5.1.2   | Constraint representation              |       |      |

|   |               | 5.1.3   | CSP-based ATPG problem formulation     |       |      |

|   | 5.2           | Advan   | ntages of the constraint technique     |       | 46   |

|   | 5.3           |         | rchical support                        |       |      |

|   |               | 5.3.1   | Hierarchical options in BudaTest       |       |      |

|   |               | 5.3.2   | Problems in CTDF expansion             |       |      |

|   | 5.4           | Contro  | ol-dominated and sequential circuits   |       |      |

|   |               | 5.4.1   | Control-dominated circuits             |       |      |

|   |               | 5.4.2   | Sequential modelling                   |       |      |

|   | 5.5           | Array   | selection                              |       |      |

|   | 5.6           |         | model                                  |       |      |

| 6 | CSI           | P solut | tion                                   |       | 55   |

| • | 6.1           |         | racking in BudaTest                    |       |      |

|   | 6.2           |         | ard techniques                         |       |      |

|   | 0.2           | 6.2.1   | Implication                            |       |      |

|   |               | 6.2.2   | Interval, masked and set logic         |       |      |

|   | 6.3           |         | umping                                 |       |      |

|   | 6.4           | _       | uninterpreted search                   |       |      |

|   | 0.4           | 6.4.1   | Node classification                    |       |      |

|   |               | 6.4.1   | Colouring goals                        |       |      |

|   |               | 6.4.2   | Token semantics                        |       |      |

|   |               | 6.4.4   | Constraints in the colouring domain    |       |      |

|   |               | 6.4.4   | Correctness of the colouring search    |       |      |

|   |               | 0.4.0   | Collectness of the colouring search    | <br>  | - 00 |

CONTENTS

|              |     | 6.4.6   | A colouring example                                   | 67  |

|--------------|-----|---------|-------------------------------------------------------|-----|

|              |     | 6.4.7   | The handling of fan-outs, indexing and slicing        | 68  |

|              | 6.5 | Result  | evaluation                                            | 70  |

|              |     | 6.5.1   | Evaluation of implication-related techniques          | 71  |

|              |     | 6.5.2   | Backjumping performance                               | 72  |

|              |     | 6.5.3   | Evaluation of the type-uninterpreted search technique | 73  |

| 7            | Maı | nufactu | uring test on the wafer                               | 76  |

|              | 7.1 | Diagno  | osis terms and wafer-scale testing                    | 77  |

|              | 7.2 | Evalua  | ation of the syndrome                                 | 78  |

|              | 7.3 | Impact  | t of comparator faults                                | 79  |

|              | 7.4 | Pre-dia | agnosis comparator test session                       | 80  |

|              | 7.5 |         | tolerant result observation                           |     |

|              | 7.6 | Fault t | tolerant comparison model                             | 87  |

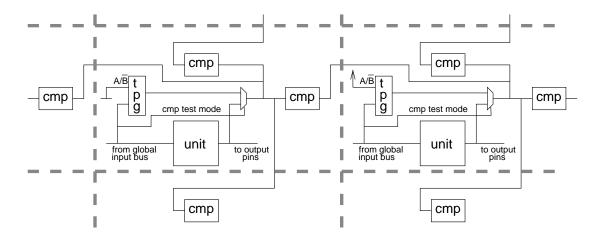

|              | 7.7 | Wafer   | implementation                                        | 88  |

| $\mathbf{A}$ | Ben | chmar   | k circuits                                            | A-1 |

|              | A.1 | Gate-le | evel circuits                                         | A-1 |

|              |     | A.1.1   | Adder family                                          | A-1 |

|              |     | A.1.2   | ISCAS'85 family                                       | A-2 |

|              | A.2 | High-le | evel benchmarks                                       |     |

|              |     | A.2.1   | Combinational multiplier                              |     |

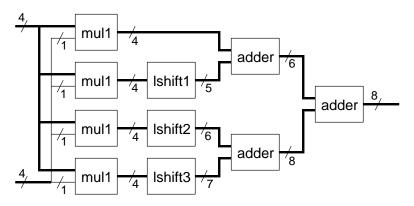

|              |     | A.2.2   | Greatest common divisor                               |     |

|              |     | A.2.3   | Bubble sort                                           |     |

| $\mathbf{B}$ | The | Buda'   | Test program                                          | B-1 |

# List of Figures

| 1.1 | In-circuit and functional testing of a board                      | 9  |

|-----|-------------------------------------------------------------------|----|

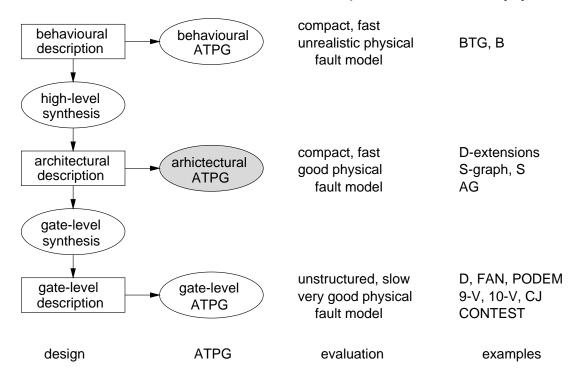

| 2.1 | Digital design flow                                               | 14 |

| 2.2 | Architectural style                                               | 16 |

| 3.1 | Active s-a-1 and wired-or short fault                             | 20 |

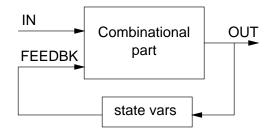

| 3.2 | General sequential circuit                                        | 24 |

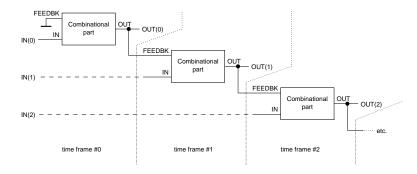

| 3.3 | Iterative combinational model of a sequential circuit             | 24 |

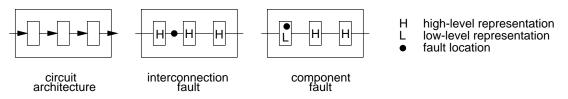

| 3.4 | Use of high and low-level models                                  | 28 |

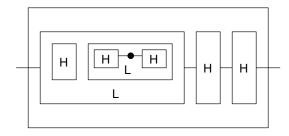

| 3.5 | Recursive application of the hierarchical principle               | 28 |

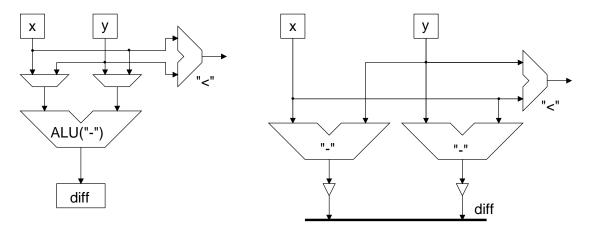

| 3.6 | Different architectures of the same behavioural source            | 30 |

| 3.7 | Comparison of ATPG entry points                                   | 31 |

| 4.1 | Constraint network hypergraph representation                      | 34 |

| 4.2 | Exemplary decision tree                                           | 37 |

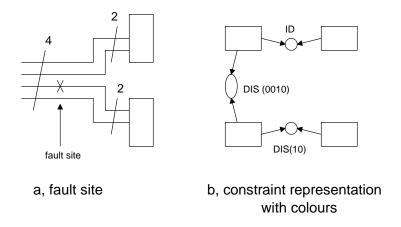

| 5.1 | ATPG problem represented as a constraint network                  | 46 |

| 5.2 | Symmetric constraints                                             | 47 |

| 5.3 | Network flattening                                                | 48 |

| 5.4 | Representation of stuck-at faults of wide signals                 | 53 |

| 6.1 | Phases of Sziray's node classification                            | 62 |

| 6.2 | Large proportion of duplicated variables                          | 62 |

| 6.3 | The colouring and the typed domains                               | 63 |

| 6.4 | Two phases of CSP solving                                         | 64 |

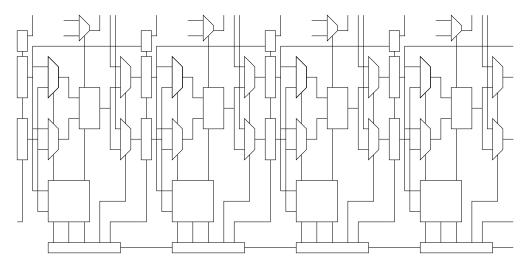

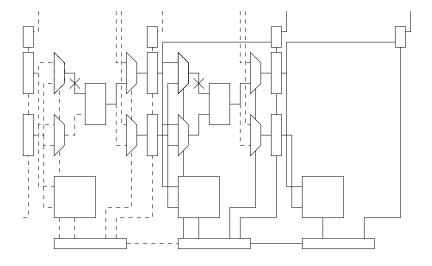

| 6.5 | GCD in 4 frames, all variables in two instances                   | 68 |

| 6.6 | GCD in 4 frames, some variables eliminated by node classification | 68 |

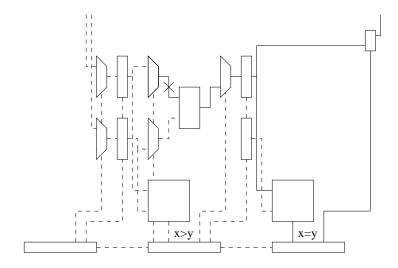

| 6.7 | GCD in 4 frames, many variables eliminated by colouring           | 69 |

| 6.8 | The effect of UNKNOWN (input)                                     | 69 |

| 6.9 | Auxiliary information used in D-propagation                       | 70 |

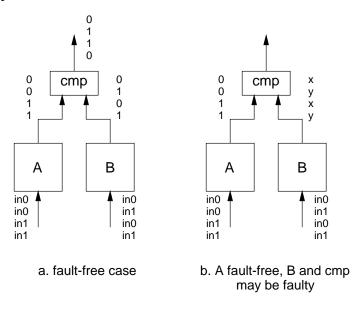

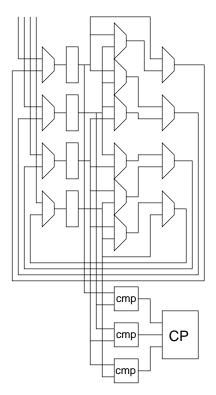

| 7.1 | Faulty chips                                                      | 79 |

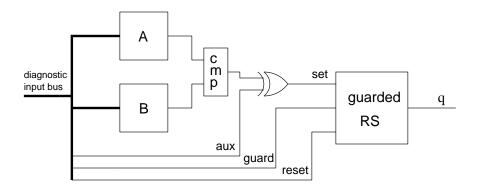

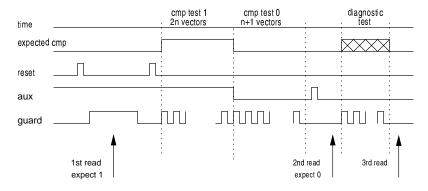

| 7.2 | Comparator slice test session                                     | 81 |

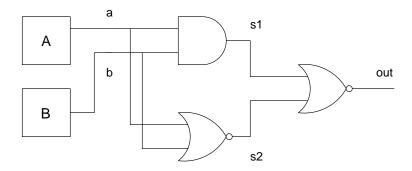

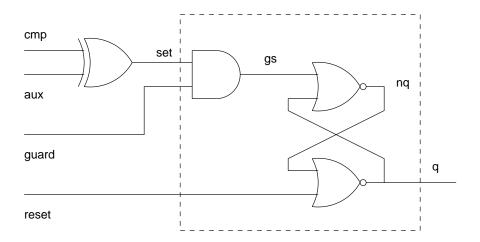

| 7.3 | A simple 1-hit comparator                                         | 82 |

LIST OF FIGURES vii

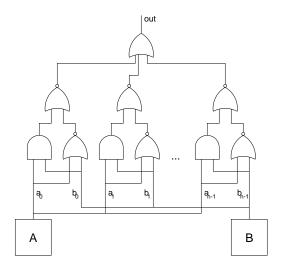

| 7.4 | A simple n-bit comparator             |

|-----|---------------------------------------|

| 7.5 | Syndrome collection circuitry         |

| 7.6 | Complete test                         |

| 7.7 | Syndrome collection at the gate level |

| 7.8 | Non-identical chips on the wafer      |

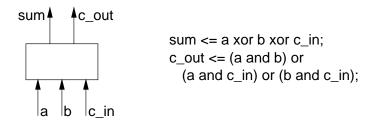

|     | Full adder                            |

| A.2 | n-bit adder                           |

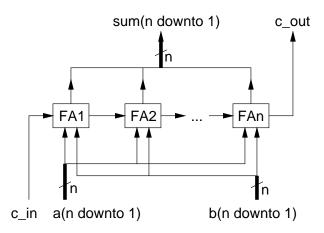

| A.3 | 4-bit combinational multiplier        |

| A.4 | Greatest common divisor               |

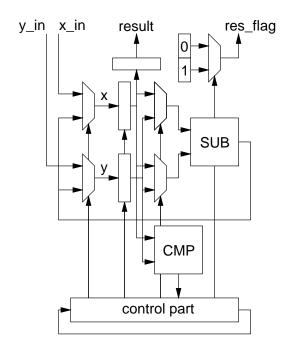

| A.5 | Bubble sort                           |

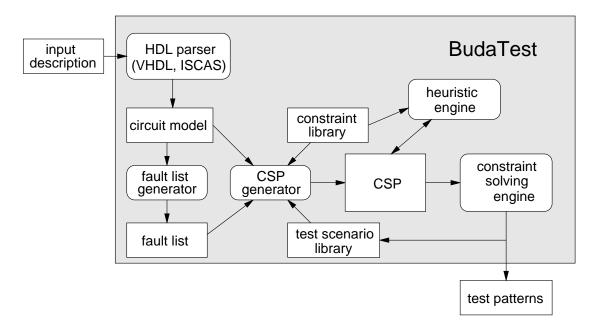

| B.1 | BudaTest block diagram                |

# List of Tables

| 1.1 | Comparison of different ATPG approaches             | 5           |

|-----|-----------------------------------------------------|-------------|

| 1.2 | Advantages $(+)$ and drawbacks $(-)$ of WST methods | 7           |

| 1.3 | Various testing aspects                             | 10          |

| 2.1 | Features of representation levels                   | 18          |

| 3.1 | Meaning of composite values in the D algorithm      | 21          |

| 3.2 | D propagation table of an OR gate                   | 21          |

| 4.1 | CONTEST results                                     | 42          |

| 5.1 | Effect of limited CTDF size on the fault coverage   | 50          |

| 5.2 | A constraint representing a wired-and short fault   | 53          |

| 6.1 | Intersection results                                | 60          |

| 6.2 | 2-to-1 multiplexer colour set                       | 65          |

| 6.3 | Multiplier colour set                               | 66          |

| 6.4 | Implication performance for different techniques    | 72          |

| 6.5 | Backjumping performance                             | 73          |

| 6.6 | Effect of node classification and colouring         | 74          |

| 7.1 | Invalidation rule in the PMC model                  | 77          |

| 7.2 | Violations of the Chwa-Hakimi model                 | 80          |

| 7.3 | Impact of the behaviour of B                        | 81          |

| 7.4 | Single-bit comparator faults and detecting patterns | 82          |

| 7.5 | Test patterns for $n$ slice                         | 83          |

| 7.6 | Gate level fault coverage of the test               | 87          |

| 7.7 | Refined comparison model                            | 88          |

| A.1 | The adder family                                    | <b>A</b> -2 |

| A.2 | The ISCAS'85 family                                 | A-2         |

| A.3 | The multiplier family                               | <b>A</b> -3 |

| A.4 | The GCD family                                      | <b>A</b> -5 |

| A.5 | The bubble sort family                              | 4-6         |

### Chapter 1

### Introduction

The appropriate testing of manufactured components is an essential requirement in the electronics industry, especially in applications requiring highly reliable devices. Since an electronic device can be damaged during manufacturing, assembly, or normal use due to physical faults, the detection of faults is crucial in any phase of the life cycle of the device. In special applications the erroneous behaviour of a faulty component may sometimes cause inestimable damage in the system. Even if the damage is moderate, the early detection of faulty components should always have an important priority.

#### 1.1 Cost factors in testing

It is evident that testing must be carried out for a circuit after its production or occasionally during its lifetime, even if testing is costly.

We will examine the cost and the quality of the test by identifying some important cost factors, mainly from the point of view of *test patterns*. Note that other cost factors exist, e.g. those related to the applied test technology. However, the cost components listed below are important in every technology.

The prerequisite of every testing method is a proper set of test patterns. The selection of the test patterns has a crucial impact on the test quality, and therefore on the testing cost as well. We will place emphasis on the following aspects:

- test development time: The time required to generate the test patterns. The test patterns need to be developed only once for a given circuit, therefore the relative cost of test development depends on the testing volume.

- test execution costs: These cost factors apply every time an instance of the given circuit is tested.

- fault coverage: This feature shows what proportion of physical faults from

a given fault model is detected by the test sequence. The cost of faults not

covered by the test includes the damage caused by the possibly faulty circuit,

or the cost required for testing the faulty component at a higher structural level. It is a common rule in the testing industry that the detection of a fault in a component becomes an order of magnitude more expensive when the component is built in a larger system than when it is tested as a stand-alone circuit.

The fault coverage is highly related to the test development time. Obviously, the higher fault coverage is required, the more time is spent with the more accurate test computations.

- test size: The space required to store the test patterns.

- **test execution time:** The time required to apply the patterns. This feature is often proportional to the test size, but can also significantly differ, e.g. when test patterns are generated by a certain algorithm (or randomly).

Placing emphasis on different aspects leads to different test strategies. The applied strategy depends on the testing environment and objectives. For example, random test patterns involve negligible test computation time and storage space. However, the fault coverage may remain severely limited (especially in case of sequential circuits), while the test application time can be long due to redundant vectors that actually do not detect any fault. In large systems fault coverage is a much more important issue than little storage space, and in highly dependable systems it becomes particularly crucial. In order to obtain a high fault coverage a test pattern generator (TPG) algorithm is required whose task is to find test patterns for given faults with a guaranteed lower bound on the fault coverage. Certainly, deterministic TPG entails that test computation time increases significantly. It should be noted that test patterns are computed only once for a circuit, therefore a high-volume production can decrease relative test computation time.

#### 1.2 Problem statement and contribution

The present thesis aims at the reduction of the costs that correspond to the test quality aspects described above. The following cost factors are addressed:

1. test computation time and fault coverage: I have developed a high-level circuit modelling style and automatic TPG (ATPG) which can efficiently handle high-level digital circuits appearing in the engineering practice. The method provides higher fault coverage under the same time constraints, or, equivalently, can reach a similar fault coverage in a shorter time than traditional gate-level ATPG algorithms. In parallel with this performance improvement, the proposed ATPG method provides much better interface to existing high-level computer-aided design (CAD) methodologies and tools.

2. **test execution time:** I propose techniques that improve the applicability of an existing wafer-scale testing (WST) idea. In contrast to traditional manufacturing testing which performs chip tests one by one, diagnosis-based WST allows for their parallel execution. This method is, however, very susceptible to the physical faults of certain additional circuitry which is assumed to be fault-free. The techniques proposed in this work provide fault-tolerant features for the diagnosis-based WST method.

#### 1.2.1 Test computation goals

Logic design and CAD systems have undergone a rapid development in the past ten years. Not only the designed circuits became larger by orders of magnitude (in terms of transistor number), but the abstraction level of circuit descriptions was pushed increasingly higher thanks to the sophisticated CAD tools. This improvement has made traditional (gate-level) ATPG algorithms obsolete and out-of-date. The main problems with these algorithms are the following:

- They suffer very much from the exponential nature of ATPG, an NP-complete problem, as proved by Fujiwara [1]. Gate-level ATPG can be in practice applied to combinational circuits consisting of at most a few thousand gates, or to sequential circuits of a much smaller size.

- They are rather awkwardly interfaced with CAD systems. They require a gatelevel circuit description, which in many cases does not appear at all in the design flow, since the design target library is not necessarily a gate library.

On the other hand, an unquestionable advantage of the gate-level tools is their accuracy in the area of fault modelling.

It is commonly accepted in the TPG community that the gate-level efficiency problems can be significantly reduced by raising the abstraction level of TPG. In addition to the advantages of CAD-conform circuit models, another gain expected from high-level ATPG tools is faster operation. The high-level ATPG algorithms can exploit that structured high-level descriptions are not simply a large set of unstructured bit signals and gates. Since many bits of signals of wide word lengths can be handled together and large clusters of gates can be regarded as a single component, the ATPG steps can be performed in a significantly smaller problem space. In addition, as control and data signals are explicitly separated, data and fault propagation features of the circuit can be much better revealed.

However, there is no general agreement on the new ATPG entry level. Many high-level approaches exist that use the so-called *behavioural* description level as the basis for TPG. Unfortunately, fault modelling in these approaches is ambiguous or even inappropriate for certain physical fault classes.

I have chosen the architectural circuit description level as the ATPG entry point. Architectural descriptions are structural descriptions with abstract data and high-level components. TPG at this level is as efficient as at the behavioural level due to the compactness of the model, and fault modelling is as accurate as in gate-level tools. It will be shown that component interconnection faults can be directly modelled, while the faults internal to components can be handled by hierarchical modelling.

In spite of the variety of existing approaches at this level, there is a lack of methods that could efficiently handle data-dominated high-level circuits with intensive data manipulations. Some of the existing approaches are limited to special circuit types (microprocessors or logic controllers), while others have difficulties with handling intensive data dependencies.

BudaTest, the architectural ATPG method and tool proposed in this work, is intended to meet the need for a general approach that is capable of handling circuits with wide data signals and intensive data manipulation.

BudaTest uses constraint-based circuit and fault modelling. The approach owes much to CONTEST, a constraint-based gate-level ATPG tool proposed by Tilly [25]. He has proven the applicability and the efficiency of the constraint mechanism in gate-level TPG [26].

BudaTest focuses on the following questions:

• What modelling problems arise when the constraint based modelling is applied to typical architectural circuits? How to represent wide domains and high-level component descriptions? What are the other new features in architectural representations, and how to model them?

Chapter 5 deals with this problems. I identify the modelling aspects where gatelevel (enumeration-based) methods cannot be applied, and propose new representation techniques for them. I also identify architectural features whose satisfactory treatment by the high-level constraint model is a new feature of the methodology.

How can be exploited the high-level information that is present in architectural descriptions? What acceleration techniques do they allow?

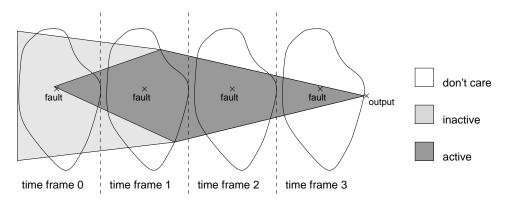

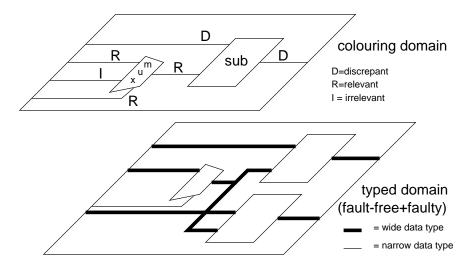

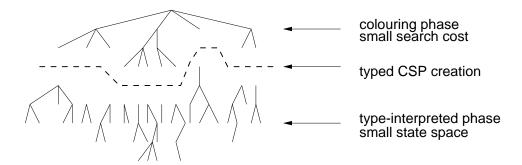

Chapter 6 discusses these issues. The exponential increase in the state space caused by the wide word length is moderated by a type-uninterpreted, token-based search technique. This technique also enables the tool to handle moderately sequential and control-dominated circuits.

BudaTest is not fine-tuned yet as long as heuristic decision control is regarded. I will show, however, that the application of non-heuristic methods that extensively exploit the high-level characteristics of the architecturally described circuit brings such improvement in terms of fault coverage and time demand that makes it a competent high-level tool.

|                 | gate-level tools | CONTEST               | $\operatorname{BudaTest}$ |  |

|-----------------|------------------|-----------------------|---------------------------|--|

| circuit level   | gate             | gate                  | architectural             |  |

| giornal tropa   | bit              | bit                   | bit, integer,             |  |

| signal type     | DIL              | DIU                   | vector                    |  |

| component set   | fix              | ${\it extendable}$    | open                      |  |

| component       | table            | DBCN                  | rule-based                |  |

| representation  | table            | DBCN                  |                           |  |

| foult model     | fix              | fix                   | library-based             |  |

| fault model     | (s-a, short)     | (s-a)                 | incl. s-a and short       |  |

| a l manit la ma | £                | constraint solving    | constraint solving        |  |

| algorithm       | fix              | $({ m customisable})$ | $({\it customisable})$    |  |

Table 1.1: Comparison of different ATPG approaches

#### 1.2.2 Contribution of BudaTest

BudaTest is an architectural TPG method and tool applicable for highly data-dependent and moderately control-dependent circuits. Its operation is based on the same constraint-based principles as those in CONTEST, but the following features are present only in BudaTest:

- Abstract-typed signals are supported.

- The rule-based high-level representation of components is solved. The component library is open. The extension of the constraint library requires only the programming of a single function in a high-level language (C++).

- The accurate modelling of low-level physical faults in the high-level circuit model is solved by defining single-bit interconnection faults and using hierarchical modelling. The coverage of the gate-level *stuck-at fault model* is proven.

- The modelling problems of using *partially wired signals* (half-words, indexed bits etc.) are solved.

- The high-level data and discrepancy propagation information present in the architectural description is heavily exploited.

Table 1.1 summarises the differences between general gate-level tools, CONTEST, and BudaTest.

#### 1.2.3 Test execution goals

Chapter 7 deals with test execution issues in the environment of wafer-scale testing (WST). WST takes place after the production of integrated circuits (ICs) and before the

packaging of good chips. Thus WST is a specific test execution environment, but is also the most typical one with a very high testing volume.

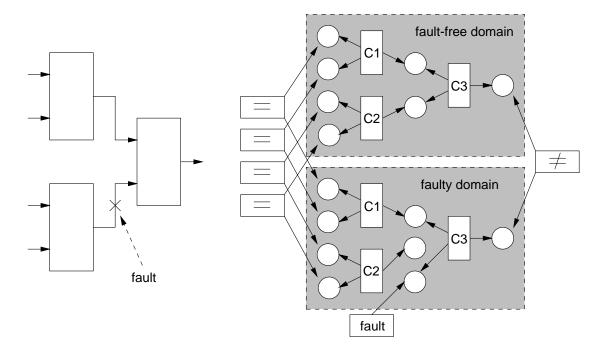

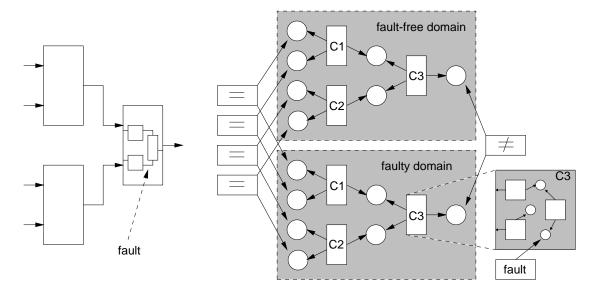

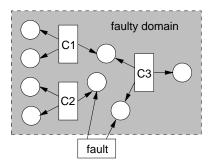

A recent idea in the post-manufacturing test of ICs is to replace traditional automatic test equipment (ATE) based testing with a concurrently executable comparison-based test of the chips on the wafer. The comparators are wired to the IC outputs and compare the IC responses for identical inputs. The comparison outcomes are evaluated by a subsequent diagnosis algorithm. The diagnosis algorithm regards the entire wafer as a single system and the ICs as the components of this system. Since the resolution of the diagnosis is exactly the chip level, the system diagnosis consists in identifying the individual chips as fault-free or faulty using the downloaded comparison results (the diagnostic syndrome).

The following list and Table 1.2 show the advantages, drawbacks and problems of the diagnosis-based testing technique compared to the traditional testing method.

- The ATE performs testing by positioning the ATE pins on the wafer chip test points and executing the test chip by chip. Diagnosis-based testing can be performed in parallel. This is an important advantage of diagnosis-based testing, especially when the chip test is long or the number of chips is large.

- At-speed testing is frequently difficult with the ATE, because the disturbance caused by the present ATE may be important when the chips operate at high frequencies. Diagnosis-based testing has no such problems.

- The hardware cost in ATE-based testing is represented by the usually extremely expensive ATE. The ATE machinery must be very accurate in the timing of driven and observed pins and in the physical positioning.

- Diagnosis-based testing needs no reference responses while ATE-based testing does.

- The cost of diagnosis-based testing consists in the area overhead caused by the dedicated circuitry required to execute the comparisons. This circuitry is present in every produced chip. It includes the comparators, comparison collectors, and the wires implementing pattern distribution and result collection.

- The test results of the ICs tested with an ATE do not depend on factors other than the coverage of the executed IC test. In diagnosis-based testing, they depend on the number and distribution of faulty chips as well. Since the classification of ICs depends on the comparisons, incorrectly diagnosed chips may entail that other chips become also wrongly diagnosed. Moreover, the correctness of the entire diagnosis algorithm depends on the validity of the applied diagnostic invalidation rule, which prescribes what outcomes are possible between components of fault-free or faulty states.

|                    |   | ATE-based        |   | diagnosis-based            |

|--------------------|---|------------------|---|----------------------------|

| execution time     | _ | sequential       | + | parallel                   |

| ATE required       | - | yes              | + | no                         |

| reference required | - | yes              | + | no                         |

| speed problems     | - | may be           | + | no                         |

| IC area overhead   | + | no               | _ | yes                        |

|                    |   | IC test coverage |   | IC test coverage           |

| 1: 1:4:-1          |   |                  | _ | number of faulty ICs       |

| validity risks     |   |                  | _ | distribution of faulty ICs |

|                    |   |                  | _ | invalidation rule          |

Table 1.2: Advantages (+) and drawbacks (-) of WST methods

In my view the problems related with validity issues prevent diagnosis-based testing from becoming popular. The number and distribution of faults is not a crucial problem, because there exist diagnosis algorithms that give realistic bounds under any fault distribution for the correctness, provided that the number of faults does not exceed a certain limit. This limit is usually high enough and the possibly low yield of the IC technology does not endanger the validity.

However, all diagnosis algorithm require that the applied invalidation rule not be violated because of "malicious" faults in the dedicated circuitry. A valid diagnostic rule is even more important than good IC test coverage because of the following:

- A chip containing a fault that is not covered by the IC test will pass the test, but the diagnostic incorrectness for this chip does not influence the correct or incorrect classification of other chips.

- Since the diagnostic algorithm uses the adjacent chips as references, incorrectly diagnosed chips may involve that adjacent chips are also wrongly diagnosed. A comparator fault frequently implies the wrong diagnosis of some local chip even if the IC test is very good, and this local incorrectness can be propagated wafer-wide without limits.

In spite of this serious weakness, there are no diagosis-based WST approaches that are applicable for general ICs and take into account this validity risk.

#### 1.2.4 Contribution in WST

This dissertation concentrates on fault-tolerant issues of the WST technique. A test session is proposed that is dedicated to the comparators and the comparison compression circuitry. It is formally proven that the test session detects any combination of multiple stuck-at faults in this circuitry. The diagnostic model is refined to include reliable and

unreliable comparisons. A wafer-scale scheme is proposed to meet the requirements of the dedicated circuitry test.

#### 1.3 Environment and terminology

This section gives a short introduction to the terminology and some testing aspects of electronic circuits. A second goal of this classification is to set the scope of this work in the various test-related areas.

- digital vs. analogue. In digital testing, the values in the used circuit mode are have all discrete ranges. The analogue and continuous output measured during testing is quantised into discrete time and discrete values which must match exactly the expected values to pass the test. Digital testing has the property that the number of possible circuit states is finite. In analogue testing analogue-type outputs must remain within a specified range.

- We deal with digital testing in this dissertation. We note that the data-dominated nature of BudaTest allows for a moderate extent of quantisation of analogue signals, although the size of the resulting problem space inhibits its use for larger circuits.

- We propose the fault-tolerant techniques for digital WST. Diagnosis-based WST is applicable to analogue testing as well, but analogue comparators should be designed with care, and the presented fault-tolerant features apply for the digital part of the diagnostic circuitry.

- physical vs. design faults. Testing against design errors has many common features with testing against physical failures, but the set of design errors is not defined as exactly as in a physical fault model.

- We always assume physical faults in this thesis.

- permanent vs. transient or intermittent. Permanent faults entail deterministic circuit behaviour in digital circuits while the circuit behaviour depends on whether or not transient or intermittent faults are present. Permanent faults are usually detected by dedicated post-manufacturing or maintenance off-line test sessions. Transient or intermittent faults are not detected by precalculated test patterns. Instead, fault-tolerant systems are protected against such faults by various on-line error detection mechanisms (watchdogs, error detection/correction codes, master/checker configurations etc.), which are methods based on information redundancy.

- In accordance with these principles, the goal of the testing in this work is the detection of permanent faults.

- deterministic vs. random TPG. Practical ATPG usually starts with random TPG and the random phase is terminated when the generated random vectors do not detect enough untested faults. At this point, the only way to increase fault coverage is launching a deterministic ATPG algorithm which searches for test patterns using the circuit model and assuming specific target faults.

- The BudaTest approach addresses efficiency issues of deterministic TPG.

- detection vs. diagnosis. There exist testing approaches aiming at system diagnosis. The goal of diagnostic tests is not merely the detection of the presence of faults, but the identification of the faulty part as well. They are typically performed in multi-component systems to find faulty components to replace, but they can be useful in the IC technology as well, inasmuch as they help identify critical design or manufacturing problems.

- We do not address diagnostic issues in this work.

- Note that the diagnosis-based WST approach is an interesting mixture of diagnosis and detection where the detection test of the chips is performed as the diagnostic test of the wafer. The proposed fault tolerant technique can be used by any wafer diagnosis algorithm.

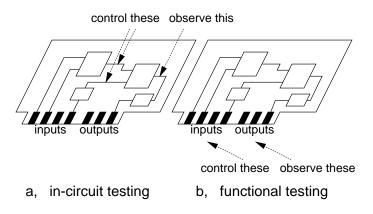

- functional vs. in-circuit. According to the tester's access to internal points of the device, we can distinguish between in-circuit and functional testing (Figure 1.1). In in-circuit testing the tester can drive and observe the internal points of the tested circuit. Since components can be isolated and tested independently, the ATPG and testing tasks can be decomposed into several small and combinational tasks. In functional testing, the circuits are driven at their input pins and observed at their output pins, exactly like during normal operation. Since internal points are only indirectly controlled and observed, this latter type of testing requires longer and more complex test sequences.

Figure 1.1: In-circuit and functional testing of a board

| aspect        | options                                    |  |  |

|---------------|--------------------------------------------|--|--|

| fault source  | physical, manual design, transformation    |  |  |

| fault life    | permanent, transient, intermittent         |  |  |

| circuit type  | digital, analogue, mixed                   |  |  |

| ATPG kind     | deterministic, random, pseudo-random       |  |  |

| test purpose  | fault detection, diagnosis                 |  |  |

| access type   | functional, in-circuit                     |  |  |

| testing speed | at-speed (parametric), static (functional) |  |  |

| circuit age   | manufacturing, maintenance                 |  |  |

Table 1.3: Various testing aspects

A current trend in electronics is the increasingly frequent use of functional testing. In-circuit testing requires a costly ATE, and the rapidly growing speed and integration of devices raises other problems with the accessibility of internal points, especially in *surface-mounted* technologies.

There exist a few solutions by which a logically in-circuit test can be implemented as a functional test. Design for testability (DFT) is the comprehensive name of design solutions that provide a logical interface to physical access points. DFT techniques include test point additions and scan-based designs (including LSSD [3] and boundary-scan [4]). However, DFT is usually very expensive since it requires extra surface and additional circuit pins. Although for today's really large circuits the introduction of some DFT is inevitable, ATPG algorithms should be nevertheless improved and made capable of handling larger subcircuits, thus reducing the cost of DFT.

- Since test computation problems do not characterise the simple in-circuit tests, the BudaTest method should be used in an functional test enviropnment.

- The discussed WST technique is also a functional test, because it compares IC outputs.

Table 1.3 gives an overview about the listed and some other ATPG-related aspects. We use bold typeface when BudaTest is characterised by the given feature and italics when the feature is related to diagnosis-based WST.

#### 1.4 Outline of the thesis

This work is structured as follows:

- Chapter 1 presents the motivation of this work and lists what contributions it provides. It gives an introduction to ATPG-related terminology and sets the scope of the proposed approaches.

- Chapter 2 describes the current trends and status of digital design. It describes the design process and explains its stages from the point of view of test generation.

- Chapter 3 gives an overview on existing ATPG approaches. First, gate-level algorithms and their enhancement schemes are discussed. Then existing architectural and behavioural TPG approaches are presented together with their advantages, drawbacks and main application fields.

- Chapter 4 describes what constraints are and how constraint satisfaction problems can be solved. It draws attention to the efficiency-related issues of the solving algorithms and gives an overview what main enhancement ideas the constraint literature provides. The chapter also presents an existing constraint-based gate-level ATPG approach.

- Chapter 5 identifies modelling problems that must be solved if we want to raise the abstraction level of TPG. It shows how BudaTest handles these problems.

- Chapter 6 presents the constraint solving engine incorporated in the BudaTest tool. It describes how high-level circuit information is exploited by the ATPG-specific solver, and presents performance data measured on high-level and low-level benchmark sets.

- Chapter 7 deals with the fault-tolerant issues of the diagnosis-based WST approach. Since this chapter is not directly related to the previous chapters, a short introduction is given about the diagnosis literature. Then a specific circuitry test is proposed which is gradually extended until it covers all important parts of the diagnosis-related circuitry. A wafer template that allows for the execution of the fault tolerance test is also shown.

- **Appendix A** describes the benchmark circuit set used for performance measurement.

- **Appendix B** briefly introduces the structure and interface of the BudaTest program.

The dissertation is usually written in passive or plural first person. I use singular first person whenever I want to emphasise my personal contribution.

### Chapter 2

## Current trends in digital design

Since testing in inseparable from design issues, we summarise what major trends apply in digital design.

It is probably needless to emphasise in what extent the integration of circuit components improves, and, consequently, the number of transistors in a single unit grows. In the sixties and seventies when the ATPG methodology was developed, the terms small, medium, large and very large scale integration (SSI, MSI, LSI, VLSI), ranging from dozens to thousands of transistors on a surface unit, was a meaningful distinction between technologies. Now we speak of millions of transistors in a single chip, and this quantity doubles about every three years [5].

#### 2.1 CAD tool features

With the increase in size and integration, design methodologies have undergone a fast development in the past ten years. It was initially the engineer's job to carry out the entire design procedure from the specification until the circuit lay-out. As the result of CAD methodology improvement, ad hoc designs of any complexity have been replaced by structured design techniques where the majority of tasks are automated. The methodology, implemented by state-of-the-art CAD tools (e.g. Cadence, Synopsys, Mentor [6, 7, 8]), are characterised by the following main features:

- Hardware synthesis is based on design libraries, which contain existing components provided by the CAD tool vendor or generated by the user. The libraries promote intellectual property (IP) reuse. Their use decreases the development time significantly, because the library elements do not need to be redesigned.

- The design direction is top-down. The goal of the digital design procedure is to gradually refine the initial specification into a structural description of utilised library elements. Accordingly, the design process consists of several stages represented by increasingly detailed and decreasingly abstract descriptions of the same circuit.

- The tasks that can be automated are passed from the engineer to the tool. As a result of a continuous improvement, the automatic entry point moves toward more and more abstract description levels. Silicon compilers that appeared about fifteen years ago transform a satisfactorily detailed structural description into layout plans. A recent improvement is the appearance of high-level synthesis (HLS) tools (e.g. AMICAL [9]) which push the automatic design entry point even higher in abstraction. They are capable of processing behavioural register transfer level (RTL) descriptions and generating architectural descriptions. The features of these levels will be discussed later in this chapter.

- A common hardware description language (HDL) is used at every stage of the design of a circuit. The most popular languages are the IEEE standard VHDL [10] and Verilog. VHDL has a high modelling power and allows for various descriptive styles: it permits the use of procedures and even of dynamically allocated memory where only behaviour is important, but it can be also used for the mass simulation of gate-level netlists. The advantages of VHDL include the portability between CAD tools and the possibility of mixed-level simulation.

- Tasks other than logic design are automated and incorporated in the CAD tool. Such tasks include automatic or computer-assisted verification (e.g. microprocessor verification in [12]), quality evaluation, or, as in the case of this thesis, ATPG.

#### 2.2 Digital design flow

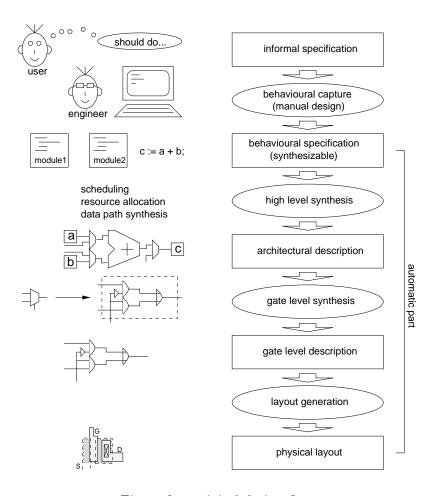

This section describes the stages of the design process which are important from the point of view of ATPG. The input of this process is the informal (and therefore ambiguous) specification of what the circuit should do, while the output is the lay-out masks directly used by the manufacturer. The intermediate stages are illustrated in Figure 2.1.

The first part of the process, denoted as behavioural capture in Figure 2.1 is actually a very complex manual task and usually consists of several substages and iterations. Large systems are first modelled at the system level by means of procedural and abstract constructs. This description can already be simulated but the used language constructs are so abstract that they cannot be automatically processed. Thus the description is manually refined and separated into smaller modules. During this transformation, many rules of thumb must be respected and the most abstract language constructs must be implemented in less abstract ways.

Since ATPG is related to the automatic part of the logic design, now we are not interested in this part. After the manual design, we reach the synthesizable behavioural level where automatic synthesis begins.

Figure 2.1: Digital design flow

#### 2.2.1 Synthesizable behavioural VHDL

This level is characterised by the following features:

- The behaviour of a component is specified as a set of *VHDL processes*, which can be complex procedures as well. Certain restrictions apply to resetting and clock usage styles.

- The use of abstract data types and complex expressions is allowed.

- Conditional statements, loops etc. are permitted.

#### 2.2.2 High-level synthesis

High-level synthesis tools read synthesizable descriptions and generate an architecture, i.e. a structure of high-level components. The main goal of HLS is to generate a structure functionally equivalent to the processes.

They go through the following basic steps:

• scheduling. The procedures in the behavioural descriptions are divided into time frames in this step. Instructions in a time frame will be executed simultaneously in one clock cycle.

The HLS output is functionally equivalent to the synthesized behvaioural description, but its timing may be different. The code can explicitly define time frame boundaries with VHDL wait statements, but the HLS tool can also introduce new frames by revealing data dependencies or by other means.

Assignment delays and other kinds of explicit time values of the behavioural specification are ignored. The exact parameters are determined by the characteristics of the library elements.

• resource allocation. VHDL operators and function calls are mapped into functional units (FUs), those components that implement the operations. There is a FU library whose elements are capable of executing one or more VHDL operations. An adder unit, for example, implements the "+" operation while a suitable ALU can be utilised wherever the VHDL parser encounters the "+", "-", and the wordwise logical operators.

Scheduling and resource allocation are complementary tasks. There are usually design options to prefer either fast or cost-effective (in terms of surface usage) design styles. A cost-driven design, for example, may define two time frames for instructions which use the same FU resource and would be executed parallelly in a speed-driven design.

- data path synthesis. This step generates the wires and defines the routing between data containers and FUs. In a multiplexer-based design, multiplexers are placed in front of multiply used FUs and before data containers that are driven by several assignments in a procedure. In a bus-based design the multiplexer outputs are replaced by buses and multiplexers are substituted with bus driver auxiliary elements.

- control flow extraction. The HLS tool creates a so-called control part in the form of a behaviourally described finite state machine (FSM). This component collects the Boolean signals coming from the data part and generates control signals such as the selector inputs of multiplexers, register write enable signals and operation codes of multi-operation FUs.

It is usually possible to define design constraints that limit the number of time frames, the circuit area, the power consumption and other various design parameters. If such a constraint is violated, a subsequent iteration may produce a different architecture.

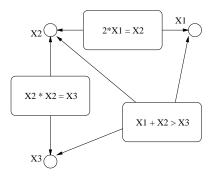

#### 2.2.3 Architectural VHDL

We call the HLS output description style *architectural*. Its main features are the following:

- It is a *structural* description, i.e. a list of components interconnected by signals.

- The signals have abstract data types (integer, bit vector, or even records) and therefore large word widths.

- The components correspond to the elements of the FU library, can be high-level and sometimes sequential. In addition, there are registers needed for data storage, and auxiliary components required for the establishment of data paths.

- The components can be parametrised. The used instance depends on the actual data size.

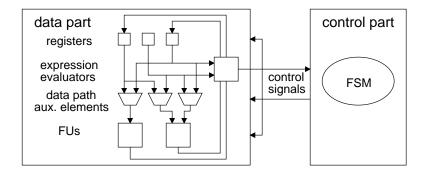

- Control and data are clearly separated (Figure 2.2). The signals within the data part are data signals and may have wide abstract types. The signals interconnecting the two parts are considered as control signals. Thus control signals include expression result signals, FU operation codes, multiplexer selectors (bus driver controls), and register control signals. Control signals have a small range.

Figure 2.2: Architectural style

#### 2.2.4 Low-level synthesis

Low-level synthesis (LLS) starts with an architectural description and generates the target of the design, usually the lay-out plans and the masks required in manufacturing. The most important tasks are the following:

• component and wire placement. This task determines the physical position of the pre-designed library elements and the wires interconnecting the components. In addition to the overall surface optimisation, a number of design rules must be respected to avoid technology-related problems.

- control part synthesis. The FSM generated by the HLS tool is implemented, e.g. with a PLD.

- parametric design, e.g. decisions on the resolution of imaging, design for power consumption etc.

From the point of view test generation, the most important feature of LLS is that decisions made during LLS do not influence the logical manifestation of the most widely assumed physical faults. A stuck-at fault (see Section 3.2.1), for example, is defined the same way for any line width and wire placement.

#### 2.2.5 Gate-level descriptions

LLS is not necessarily divided into gate-level synthesis and lay-out generation as shown in Figure 2.1, because the vendor-supplied library elements can directly contain lay-out information. We still discuss this intermediate stage, because it is important from the point of view of traditional ATPG methods.

Gate-level descriptions are the last logical and technology-independent representations of a digital circuit. The characteristics of this level are as follows:

- It is a structural description.

- Only the *bit* data type exists. Originally complex signals are encoded into a set of bit-type signals.

- The component "library" is fix, containing the basic gate types (and, or, xor, nand, nor) and basic flip-flop types (D primarily).

- The number of signals and components is enormous. It is usually hopeless to understand the function by human reading.

Table 2.1 gives a summary on some important features of the different representation levels and description styles.

|                         | system-level | behavioural | architectural   | gate-level |

|-------------------------|--------------|-------------|-----------------|------------|

| simulatable             | yes          | yes         | yes             | yes        |

| synthesizable           | no           | yes         | yes             | yes        |

| procedures allowed      | yes          | yes         | no              | no         |

| components allowed      | yes          | yes         | yes             | yes        |

| component type          | any          | any         | library element | gate       |

| data type               | abstract     | abstract    | abstract        | bit        |

| compact                 | yes          | yes         | yes             | no         |

| control-data separation | no           | no          | yes             | no         |

Table 2.1: Features of representation levels

### Chapter 3

## Previous ATPG approaches

This section gives an overview on existing ATPG approaches for digital circuits described at various levels. We divide the discussion into presenting gate-level and high-level approaches.

#### 3.1 Fault models

I devote special attention to the question of fault modelling because in my view this determines the abstraction level that can be used for ATPG.

Faults are physical failures which are caused by defective hardware material or production machinery, by incorrect design or by human error (Mourad [13]).

Logical faults change the logical function of the circuit while parametric faults modify non-digital circuit parameters such as delay, capacitance, temperature dependence etc. [1].

The fault model is the representation of the physical fault effect in a given application. Fault modelling must therefore conform to circuit modelling some way so that the fault effect can be interpreted at the level the application uses. Obviously, the relation between physical faults and the fault model must be thoroughly examined in every application that uses fault models. In particular, the following things must be proven:

- Physical faults indeed cause such a perturbation as assumed by the fault model.

- The fault model is able to represent all the expected kinds of physical faults. Certainly, we cannot take into account every imaginable fault, but the most likely ones should be listed.

#### 3.2 Gate-level ATPG

Gate-level ATPG algorithms have existed since fairly complex digital circuits appeared in the sixties. We show what basic gate-level methods exist and what improvements

have been made to traditional algorithms. Besides this overview, a good comparison of gate level methods can be found in [27].

#### 3.2.1 Gate-level fault model

The most popular logical fault model is the stuck-at (s-a) model. This fault model assumes that physical faults are manifested in the logical form that certain signals fail to hold a 0 or 1 logical value. A signal stuck at 0 (1) always carries 0 (1) even if driven with 1 (0) by a certain gate.

Though the stuck-at model is defined as signal problems, the analysis of different technologies shows that it represents fairly well component (gate) faults as well. Many internal transistor faults are equivalent to the logical s-a fault of some signal appearing in the gate-level description. We note that there are a few transistor faults in MOS technologies that cannot be represented as stuck-at faults. There exist other dedicated fault models (stuck-open, stuck-on) to cover these problems [14, 15], although they are rarely used in practice.

The *single stuck-at* fault model allows at most one stuck-at signal. The *multiple stuck-at* model allows several s-a faults to occur at the same time but the fault list is very long in this case.

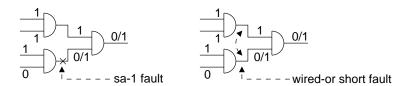

In the *short* fault model (also known as *bridging* or *coupling* faults) two signals fail to hold different values. If they would take different values in the fault-free case, the common value is determined by the used technology. Certain technologies cause *wired-or*, others cause *wired-and* relation between the shorted signals.

Figure 3.1 shows an activated s-a-1 and a wired-or short fault. Both faults cause an erroneous 1 value instead of the correct 0 at the fault location. Note that the input patterns are test patterns as well, since the circuit without the fault would produce a different response.

Figure 3.1: Active s-a-1 and wired-or short fault

Extensive studies show that test pattern sets generated for single s-a faults cover fairly well other fault types [16]. Applications that use the single s-a fault model are usually considered by the testing community as accurate in fault modelling.

#### 3.2.2 Gate-level ATPG algorithms

In the following, functional TPG algorithms will be presented. Such an algorithm finds test patterns for which the logical function modification effect of the fault becomes

| composite value                                    | fault-free value | faulty value |  |

|----------------------------------------------------|------------------|--------------|--|

| 0                                                  | 0                | 0            |  |

| 1                                                  | 1                | 1            |  |

| D (discrepancy)                                    | 1                | 0            |  |

| $\bar{\mathrm{D}} \; (\mathrm{not} \; \mathrm{D})$ | 0                | 1            |  |

Table 3.1: Meaning of composite values in the D algorithm

| input 1       | input 2       | output        |

|---------------|---------------|---------------|

| 0             | 0             | 0             |

| 0             | 1             | 1             |

| 0             | D             | D             |

| 0             | D             | $ar{	ext{D}}$ |

| 1             | 0             | 1             |

| 1             | 1             | 1             |

| 1             | D             | 1             |

| 1             | $ar{	ext{D}}$ | 1             |

| D             | 0             | D             |

| D             | 1             | 1             |

| D             | D             | D             |

| D             | D             | 1             |

| $ar{	ext{D}}$ | 0             | $ar{	ext{D}}$ |

| D             | 1             | 1             |

| D             | D             | 1             |

| D             | $ar{	ext{D}}$ | D             |

Table 3.2: D propagation table of an OR gate

apparent.<sup>1</sup>

#### The D algorithm

The first systematic ATPG approach was the D algorithm presented by Roth in 1966 [17]. As every systematic ATPG method, it is a composite simulation of the fault-free and faulty circuit. He used the 4-valued logic of  $\{0,1,D,\bar{D}\}$  to model value pairs (Table 3.1).

The gate pairs of the two simulations are handled together in a similar way. The truth table of and OR gate is given as an example in Table 3.2.

The D-algorithm consists of three basic phases:

<sup>&</sup>lt;sup>1</sup>There exist other kinds of testing which exploit parametric effects of faults.  $I_{DDQ}$  testing, for example, is based on the fact that an activated fault is likely to involve abnormal power consumption, and does not require that the fault effect be functionally visible on any output.

- 1. fault sensitisation. An activated fault is a prerequisite for successful test generation, thus this phase assigns D or  $\bar{D}$  to the faulty signal pair. The input signals of the gate driving the fault location are set to produce the negated s-a-value.

- 2. D propagation. A path is selected from the fault location to one of the outputs. The other input of the gates comprising the path are set in a way that the D or  $\bar{D}$  value can be propagated.

- 3. justification. The remaining signals are set backwards by using the gate truth tables (without the tuples containing Ds or  $\bar{D}$ s).

Since contradictions may occur, backtracking is allowed in all phases. The D algorithm does not define priorities between truth table rows when more options are available, so decisions can be regarded as random. This can lead to an unnecessarily high number of backtracks. Another problem is backtracking in the D propagation phase. If the path selection is contradictory, another D-path must be chosen. When the fault location is far from the output, the number of paths can be very large.

#### **PODEM**

Goel's PODEM [18] is the most frequently used gate-level ATPG algorithm. It is a rearrangement of D steps where decisions consist in assigning values to the input signals. Once a new input is set, the circuit is partially simulated as deep as possible.

The goals are again fault sensitisation and D propagation. The ordering of variables to assign reflects these goals. The so-called *backtrace* technique is used for selecting the variables that have the largest impact on the *target signals*. The first target signal is the fault location, then the signals constituting a selected D-path to the output are targeted. A very important feature of the algorithm is the use of *controllability measures* during backtracing and of *observability measures* during D-path selection. These measures were proposed by Goldstein [19].

The input-oriented nature of PODEM means that it is efficient for circuits with relatively few inputs, but its performance drops with the increase in the number of inputs.

#### Composite justification

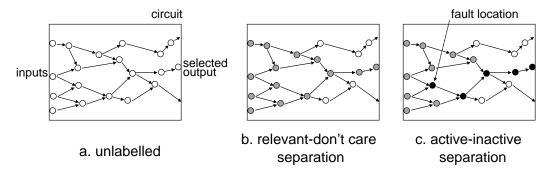

Proposed by Sziray [20] in 1979, composite justification consists of output selection and only justification steps. Once an output is selected for fault effect observation, the algorithm assigns D or  $\bar{D}$  to the output and the fault location. The rest is simply backward justification using the full tuple set of the gate truth tables, during which the signal values become determined from the output to the inputs. Since the full tuple set contains Ds and  $\bar{D}s$ , the circuit is first preprocessed in order to explore where discrepancies are admitted and what signals matter at all. This filtering technique is called node classification.

From the point of view of this work, composite justification has similar features with the approach proposed here. Although Sziray does not use constraint terminology, the lack of the path selection phase makes the entire representation uniform. Furthermore, the *node classification* technique is the first explicit technique that reveals which signals may take different values in the two simulation. The *colouring* technique presented in Section 6.4 has the same goals, although the implementation technique is rather different.

#### 3.2.3 Implication

The FAN algorithm (Fujiwara, [1]) is an improvement to D. It performs an *implication* step to explore and effectuate the value assignments that are equivalent with the most recent decision. The result of implication is a smaller subspace of unassigned wires after every decision, which necessitates fewer backtracks.

The idea of assigning implied values to signals other than the decision subject appears most explicitly in the 16-valued approach of Hegedüs [21]. Each value used by his algorithm represent a superset of the basic set  $\{0,1,D,\bar{D}\}$ . This greatly improves the implication capabilities of the ATPG tool because the exclusion of every basic value combination can be expressed. The drawback of the method is the large size of gate descriptors. Similar 9 or 10-valued logic is used in [22] and [23].

Another very important result of Hegedüs' work is the decentralised implementation of the ATPG decision engine. The mechanism of weights that can be associated to decision choices provides good support for topological measures an heuristics. He has shown that the generic algorithm may become PODEM or other algorithms by means of extreme weighting, so the algorithm can match the characteristics of the circuit it is applied to.

#### 3.2.4 Sequential extension

The basic gate-level algorithms generate single-vector tests for the faults of combinational circuits. Sequential circuits may have (and usually do have) faults which require not test vectors but sequences to detect.

There is a simple ATPG extension technique that enables combinational algorithms to cope with sequential circuits. The *iterative array* model [43] cuts the feedback loops of the sequential circuit and unrolls the consecutive time frames into a large combinational circuit (Figure 3.2 and Figure 3.3). Finding a test sequence for the sequential circuit is equivalent to finding a test vector for the unrolled circuit.

The iterative array technique is applicable when the following circuit requirements are met:

• The concept of "consecutive time frames" requires synchronous single-clock sensitivity.

Figure 3.2: General sequential circuit

Figure 3.3: Iterative combinational model of a sequential circuit

• Registers must have *reset* so that their initial value be known to the ATPG algorithm in time frame 0.

Although there are proposals in the literature aiming at the testing of asynchronous circuits without known homing sequences, this problem is rather avoided than solved.

The price of the extension is the soaring size of the ATPG problem space. The problem space of an n-frame long expected test sequence is n times larger than that in the combinational case, which is crucial in an NP-complete problem.

#### 3.2.5 CONTEST

CONTEST (Tilly, [25, 26]) is a gate-level tool that solves ATPG as a constraint satisfaction problem (CSP). We give special attention to CONTEST because the BudaTest approach presented in this work is based on the same constraint-based principle as CONTEST. CONTEST's main features are the following:

- The signal pairs of the fault-free and faulty simulation are regarded as *constraint* variables. (Section 4.1 or [27, 25] contains constraint-related definitions.)

- The function of the gate pairs is described as *constraints* over the variables.

- The variables have an initial domain of  $\{0, 1, D, \bar{D}\}$ . The actual domain of a variable describes what values can be part of a solution, which is as powerful in implication as the 16-valued logic of Hegedüs [21]. Variables are assigned locally consistent values by decisions.

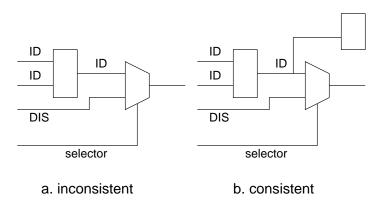

- The requirements against a test pattern are expressed by the initial domains of the variables. The initialisation of CONTEST is practically the same as that of composite justification [20], i.e. the fault location and a selected output is initialised with  $\{D, \bar{D}\}$ , and a domain preprocessing similar to node classification is performed.

- Since the field of CSP solving has an already wide literature, general CSP solving ideas are employed to speed up the ATPG process. In particular, a variation of dependency-directed backtracking (backjumping) [59] is used.

- Since all ATPG requirements are represented as constraint network data, the CSP solver has a high extent of freedom in decision control. In CONTEST, a hesitation queue is established to store decision candidates. This helps keeping decisions concentrated in one growing part of the circuit, but also leaves space for measure-based heuristics.

#### 3.2.6 Algorithm evaluation

Since there are no analytical features to which the circuits designed in practice conform, the performance evaluation of ATPG algorithms is performed by benchmarking. Besides the benchmark circuits that individual approaches propose as measurement basis, there exists a commonly accepted gate-level benchmark circuit set. The ISCAS benchmark [11], specially designed for testing gate-level related tools, contains circuits different in various aspects: different input/internal/output signal numbers and ratios, different gate numbers and ratios, tree-structured vs. highly reconvergent etc.

#### 3.3 High-level ATPG approaches

High-level approaches are characterised by an abstract model which describes the propagation and dependencies of usually abstract data. We will call *architectural* those ATPG approaches where the abstract model is in direct correspondence with the actual circuit hardware, and *behavioural* the other high-level approaches.

#### 3.3.1 Architectural approaches

#### Extensions of gate-level approaches

Many gate-level algorithms use some combination of three basic steps (fault sensitisation, D propagation, justification). There is no theoretical obstacle in defining high-level equivalents of these steps for architectural descriptions. The new methods must revise the following aspects:

• In contrast to gate-level approaches which handle the two simulations as one by defining composite values (see Table 3.1), abstract value pairs cannot be efficiently

treated as one value.

- Value tables either become very large or must be replaced with the execution of functional component procedures. Backward justification, i.e. the inversion of component procedures becomes rather difficult. For this reason, high-level PODEM which uses only forward data propagation is easier to implement [42].

- Fault modelling becomes nontrivial. Single-bit stuck-at faults, for example, affect single bits of abstract values, the effect of which must be separately defined. Internal faults of components must also be taken into account.

Many existing approaches belong to this category. The D algorithm was defined for hardware description languages in [24]. An extension for the 9-valued logic gate-level approach [23] was done by Steingart et al. in [28]. The DIAS tool [29] performs high-level composite justification (Section 3.2.2, [20]) for a dedicated hardware description language OPART [30].

In fact, the BudaTest method described in this work can be also regarded as the extension of the CONTEST constraint-based gate-level ATPG approach. Chapter 5 deals with modelling problems that are implied by the use of abstract values and high-level components. However, the extension consists not merely in the transformation of steps into abstract equivalents, but in the use of abstract algorithms which have no gate-level equivalents.

#### S-graph

S-graph based circuit representation was used by Thatte and Abraham [31], and was refined by Brahme and Abraham in [32]. The method is specific to microprocessors whose register-level model is the *system graph* (S-graph). The nodes of the S-graph represent the registers of the processor, while edges between nodes stand for instructions that move data (manipulated or not) between the registers. Two distinguished nodes, IN and OUT, model the pins controllable and observable by the external word.

The processor is regarded as a set of the following functions: register decoding, instruction decoding and control, data storage, data transfer, and data manipulation. A functional fault model is defined for each of the specified functions except data manipulation.

The faults of the register decoding, data storage and data transfer functions are tested by relatively simple algorithms which are mainly based on the topological distance of the registers from the INPUT and OUTPUT nodes. The instruction decoding and control function model was later refined in [32] and its functional faults were tested by assigning codewords to registers.

The S-graph approach is an efficient architectural method for testing general parts of microprocessors. The test generation time and the test length is polynomial with the number of registers. However, data manipulation faults are not considered and microprocessor features are heavily exploited, thus the method is hardly extendable to general digital circuits.

The S-algorithm proposed by Su et. al [33, 34] uses a similar but somewhat more general model for register transfer level descriptions. The method still assumes some explicit instruction sequence.

#### Alternative Graph

Ubar's method creates generalised decision diagrams based on the circuit and fault description [36].<sup>2</sup> Unlike in traditional algorithms dealing with binary decision diagrams [35], high and low abstraction levels as well as control and data faults are efficiently and uniformly handled by generalised DDs.

A novel concept of mixed level combining of deterministic and random techniques in test generation is introduced in AG. On the RT-level, deterministic path activating is combined with constraint techniques by means of random techniques. The gate-level local test patterns for components are randomly generated driven by high-level constraints and partial path activation solutions.

The AG approach permits test generation for finite state machines (control parts) as well [37]. For the description of functions, structure and faults in a FSM, three levels are used: functional level (state transition diagrams), logical or signal-path level, and gate level. For all these levels a uniform description language, a uniform fault model and uniform procedures for ATPG and test analysis were developed. This uniformity allows easily to move and carry partial results from level to level when solving the mentioned tasks.

The path activation and the FSM testing features of the AG approach make it an excellent method for control-dominated circuits where long and non-trivial paths and state transitions. High data dependencies are, however, not necessarily handled effeiciently due to the randomness of the solving of such subtasks.

#### 3.3.2 Hierarchical testing

Hierarchical testing is not an alternative to architectural approaches but an additional technique which allows the accurate modelling of gate-level faults.

In architectural approaches *components* and *interconnections* are meaningful terms because they reflect the circuit architecture. The different high-level ATPG algorithms generate tests for interconnection faults that appear in some way in the utilised circuit model. Thus high-level algorithms do not directly cover component faults.

High-level testing is introduced on account of the expected performance advantage due to the circuit model compactness. However, the effect of component faults cannot be generally described at the high level, because modelling physical fault effects by altered functionality is unrealistic. Thus we face two contradicting requirements:

<sup>&</sup>lt;sup>2</sup>Generalised decision diagrams were first poroposed under the name of Alternative Graphs (AG).

- 1. High-level representation is required for efficiency.

- 2. Accurate models of component fault effects can be obtained only by low-level component representation.

Hierarchical testing offers a reasonable solution for this problem by means of mixedlevel modelling. In a high-level tool supporting hierarchical testing the components have two representations:

- a high-level representation (functionally described) for efficiently representing the fault-free operation. For example, an adder component can be represented with the high-level addition operator.

- a low-level representation (structurally described), consisting of several smaller components for exact fault modelling. For instance, the same adder component can be represented with a chain of full adders. The low-level representation must conform to the design generated by the CAD tool to obtain exact fault effects.<sup>3</sup>

In the mixed-level technique, only the component affected by the assumed fault is represented with the low-level model, while others are modelled with the high-level equivalent (Figure 3.4). This way the low-level representation of certain components does not entail a dramatic increase in the component number, and the average abstraction level drops only in a minimal extent. The hierarchical principle can be applied in a recursive manner (Figure 3.5).

Figure 3.4: Use of high and low-level models

Figure 3.5: Recursive application of the hierarchical principle

<sup>&</sup>lt;sup>3</sup>In theory, functional replacement would be an alternative way to model faulty behaviour with preserving efficiency. However, as it is argued in Section 3.3.3, only a small fragment of realistic physical fault effects can be described at the high level, therefore the applicability of this concept is limited.

### 3.3.3 Behavioural approaches